PCIe参考时钟和嵌入式时钟

主板提供 100 MHz 参考时钟给显卡。显卡的 PLL 锁定到这个参考时钟,准备进入链路训练阶段。主板和显卡通过链路训练协商链路速率(如 Gen3, 8 GT/s)。链路训练依赖于参考时钟来进行同步和校准。链路建立后,数据流中的嵌入式时钟被用来同步数据传输。参考时钟继续作为备用时钟,支持低功耗模式和其他操作。当链路进入低功耗状态时,嵌入式时钟可能停止。参考时钟仍然保持工作,确保设备可以在需要时快

1. 嵌入式时钟与参考时钟的区别

嵌入式时钟

PCIe 使用的是串行通信技术,数据通过差分对(lane)以高速传输。

数据流本身包含了时钟信息,接收端通过 CDR(Clock Data Recovery,时钟数据恢复)电路从接收到的数据流中提取出时钟信号。

这种机制的好处是避免了传统并行总线中需要单独传输时钟信号的问题,从而减少了信号完整性问题和复杂性。

参考时钟

PCIe 的每个设备都需要一个独立的 100 MHz 参考时钟信号,通常由主板或根联合体提供。

参考时钟的作用是为链路初始化、同步和链路训练(LTSSM, Link Training and Status State Machine)提供一个全局的时间基准。

2. 为什么需要 100 MHz 参考时钟?

尽管嵌入式时钟可以从数据流中恢复出来,但参考时钟在 PCIe 系统中有以下几个关键作用:

(1) 链路初始化和同步

在链路启动时,发送端和接收端需要同步它们的操作。例如,链路两端的 PLL(Phase-Locked Loop,锁相环)需要锁定到一个共同的参考频率。

如果没有参考时钟,链路两端无法知道何时开始发送或接收数据,也无法正确地进行链路训练。

(2) 支持链路训练(LTSSM)

在链路训练阶段,两个设备需要协商链路速率(如 Gen1、Gen2 等)和链路宽度(如 x1、x4 等)。这些操作依赖于一个稳定的参考时钟,以确保双方能够正确协调。

例如,链路训练中的电气特性测试(如信号质量检测)需要参考时钟来校准收发器。

(3) 维持低功耗状态

PCIe 设备在空闲时会进入低功耗状态(如 L1 或 L2 状态)。在这些状态下,链路可能停止数据传输,因此嵌入式时钟也会消失。

此时,参考时钟仍然是可用的,用于维持设备的基本运行,并在需要时快速唤醒链路。

(4) 多设备共享时钟域

在 PCIe 系统中,多个设备共享同一个链路。为了确保所有设备能够在同一个时间域内工作,参考时钟提供了一个统一的时间基准。

如果没有参考时钟,不同设备可能会因为各自的时钟漂移而无法正确协同工作。

(5) 硬件实现的简化

使用一个固定的参考时钟可以简化硬件设计。例如:

发送端和接收端的 PLL 可以基于参考时钟生成所需的高频信号。

设备制造商不需要为每个设备设计复杂的时钟恢复电路。

3. 嵌入式时钟和参考时钟的关系

参考时钟是系统的基础时钟,为链路初始化和链路训练提供一个稳定的全局时间基准。

嵌入式时钟是从数据流中提取出来的时钟,用于实际的数据传输。它依赖于参考时钟的支持,尤其是在链路启动和低功耗状态下的操作。

换句话说,参考时钟是“幕后英雄”,负责确保整个系统的时序一致性,而嵌入式时钟是“前台主角”,负责实际的数据传输。

4. 总结:两者的分工

5. 举例说明

假设你正在连接一个 PCIe 设备(例如显卡)到主板上:

初始阶段:

主板提供 100 MHz 参考时钟给显卡。

显卡的 PLL 锁定到这个参考时钟,准备进入链路训练阶段。

链路训练阶段:

主板和显卡通过链路训练协商链路速率(如 Gen3, 8 GT/s)。

链路训练依赖于参考时钟来进行同步和校准。

正常工作阶段:

链路建立后,数据流中的嵌入式时钟被用来同步数据传输。

参考时钟继续作为备用时钟,支持低功耗模式和其他操作。

低功耗模式:

当链路进入低功耗状态时,嵌入式时钟可能停止。

参考时钟仍然保持工作,确保设备可以在需要时快速恢复。

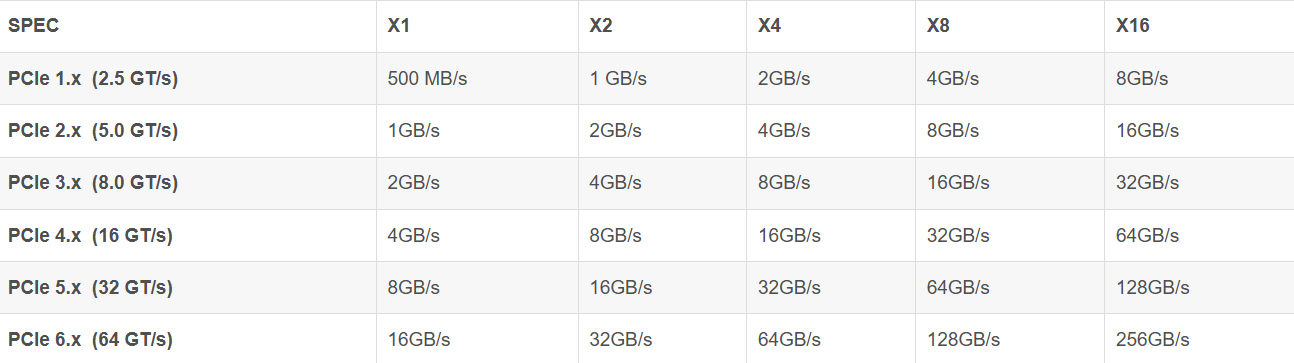

6.速率表

PCI-e2.0 协议支持 5.0 GT/s,即每一条Lane 上支持每秒钟内传输 5G个bit;因为PCIe 2.0 的物理层协议中使用的是 8b/10b 的编码方式。 即每传输8个bit,需要发送10个bit;这多出的2个bit并不是对上层有意义的信息。那么, PCIe 2.0协议的每一条Lane支持 5 * 8 / 10 = 4 Gbps 的速率。以一个PCIe 2.0 x1的通道为例(全双工是rx,tx同时发,所以吞吐乘以2),该链路的吞吐量=4GT * 2 = 8 Gbps = 1GB/s

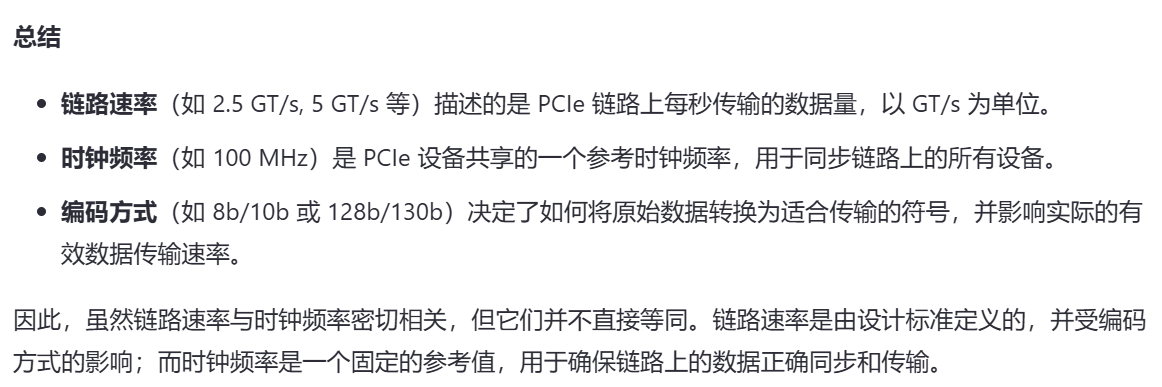

7. 结论

虽然 PCIe 使用嵌入式时钟从数据流中恢复时钟信号,但 100 MHz 参考时钟仍然是必不可少的。它为链路初始化、同步、链路训练以及低功耗模式提供了稳定的时间基准。两者分工明确,共同确保 PCIe 系统的高效、可靠运行。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)