采用vscode+iverilog进行代码编译

采用VScode来进行verilog代码的仿真和波形分析

·

参考资料

VScode编辑verilog/SystemVerilog + iverilog编译仿真 + GTKWave显示波形

https://blog.csdn.net/qq_37899920/article/details/126376878

文章目录

工具配置

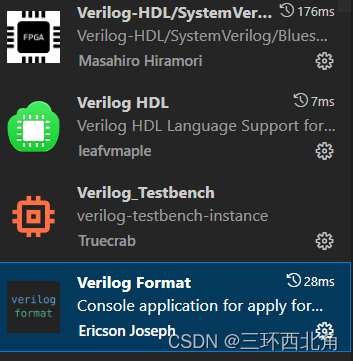

vscode中支持verilog的插件很多,安装较多的是一下几个

Verilog-HDL/SystemVerilog/Bluespec SystemVerilog:

语法高亮,代码风格检查等

Verilog HDL:

调用iverilog进行综合运行

Verilog_Testbench:

自动生成test_bench代码

Verilog Format:

verilog排版工具。

运行测试

测试的test_tb.v如下:

`include "test.v"

`timescale 1ns / 1ps

module tb_test;

// test Parameters

parameter PERIOD = 10;

// test Inputs

reg clk = 0 ;

reg [3:0] a = 0 ;

reg [3:0] b = 0 ;

reg sig = 0 ;

// test Outputs

wire [3:0] outsig ;

initial

begin

forever #(PERIOD/2) clk=~clk;

end

// initial

// begin

// #(PERIOD*2) rst_n = 1;

// end

test u_test (

.clk ( clk ),

.a ( a [3:0] ),

.b ( b [3:0] ),

.sig ( sig ),

.outsig (outsig )

);

initial

begin

$dumpfile("tb_test_wave.vcd");

$dumpvars;

#10

a=4'h0;

b=4'h0;

sig=4'h0;

#10

a=4'h1;

b=4'h0;

sig=4'h1;

#10

a=4'h0;

b=4'h1;

sig=4'h0;

$finish;

end

endmodule

实例化的模块test.v如下,这里简单的实现一个全加器:

module test(

input clk,

input [3:0] a,

input [3:0] b,

input sig,

output reg[3:0] outsig

);

always @(posedge clk or sig or a or b) begin

outsig <=(sig)?a:b;

end

endmodule

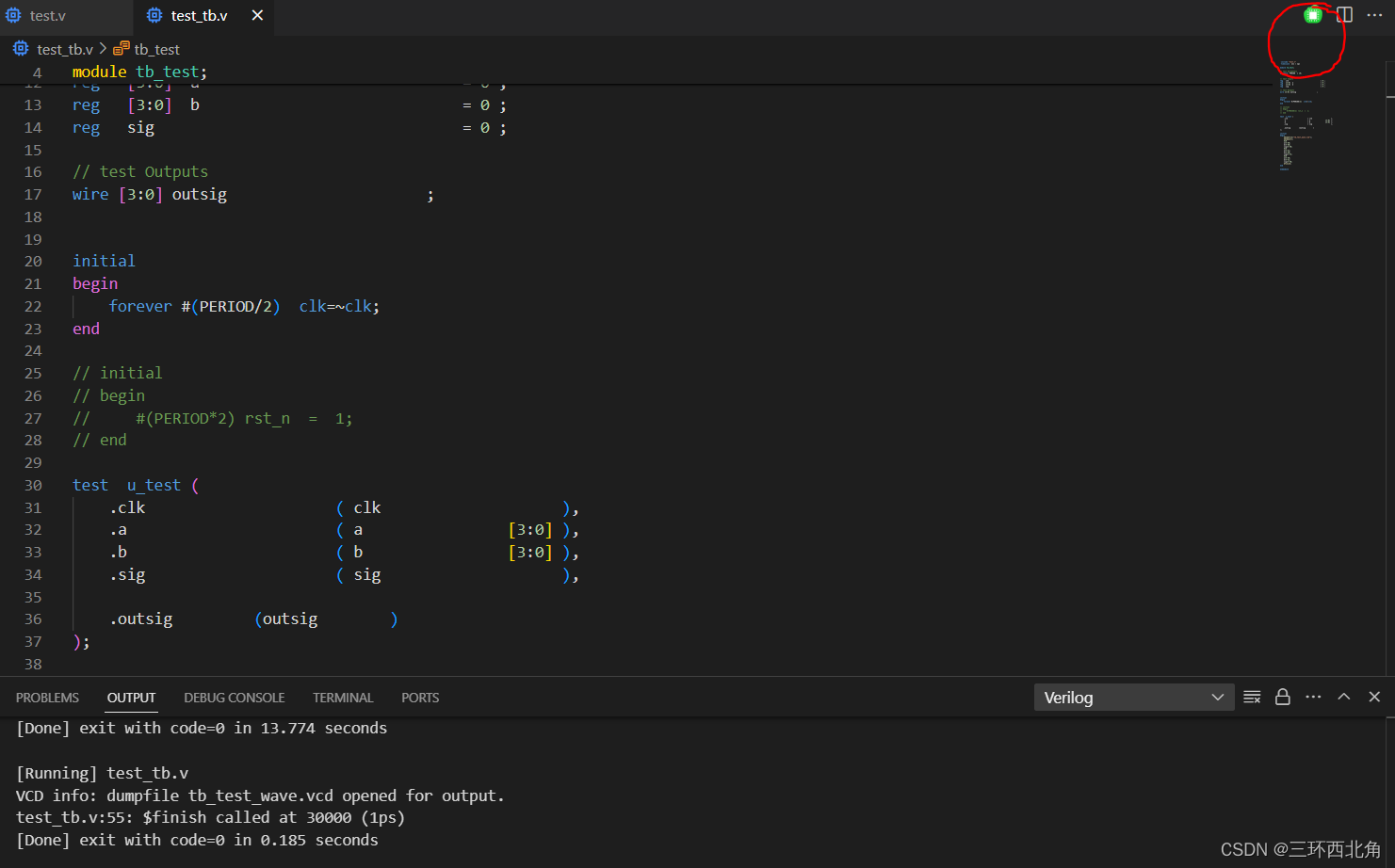

安装Verilog HDL控件后vscode右上角会有运行按钮:

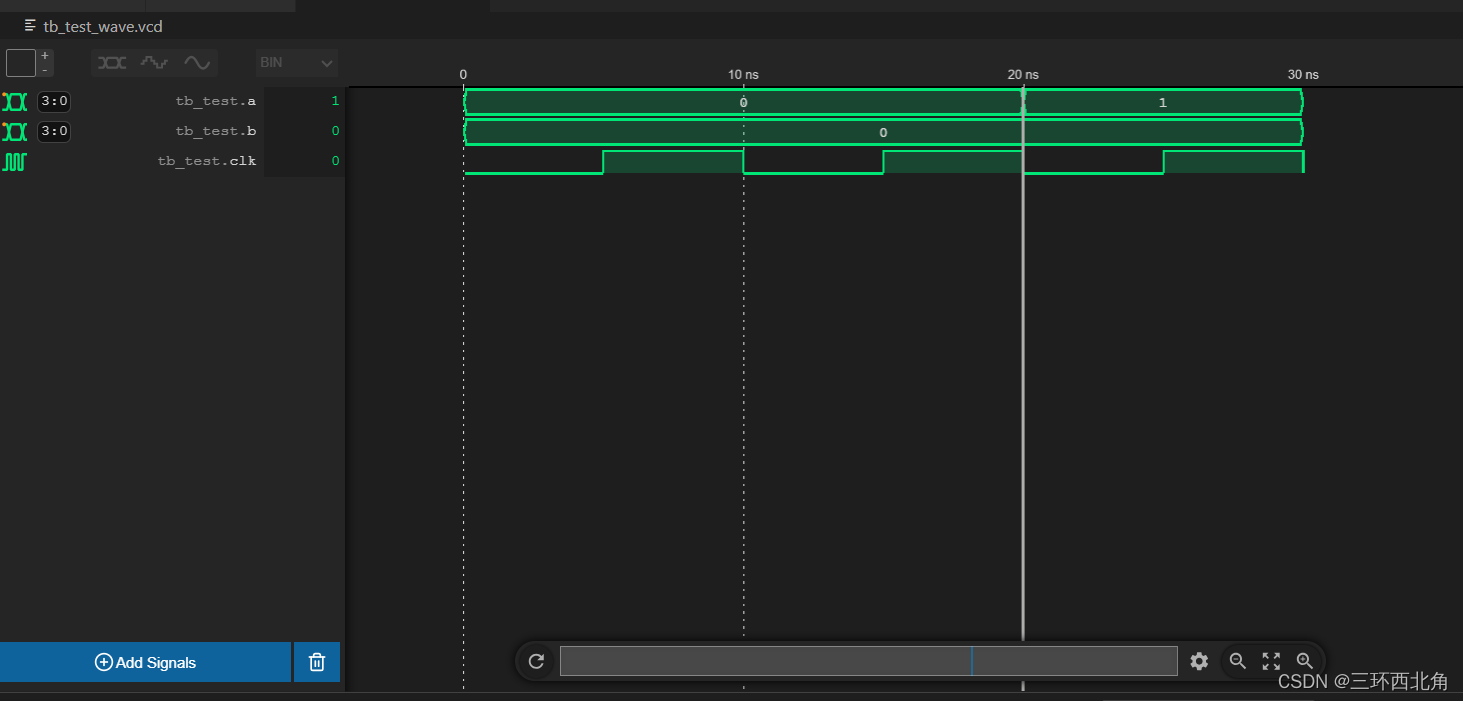

运行后生成波形文件test_tb_wave.vcd,双击即可加载波形窗口,可以添加感兴趣的波形进行观察。

关于systemverilog的编译

由于verilog hdl控件不识别systemverilog,使用systemverilog编写的tb不能直接生成波形文件,可以考虑用批处理命令调用modelsim生成波形文件后再加载到vscode进行分析的方法。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)