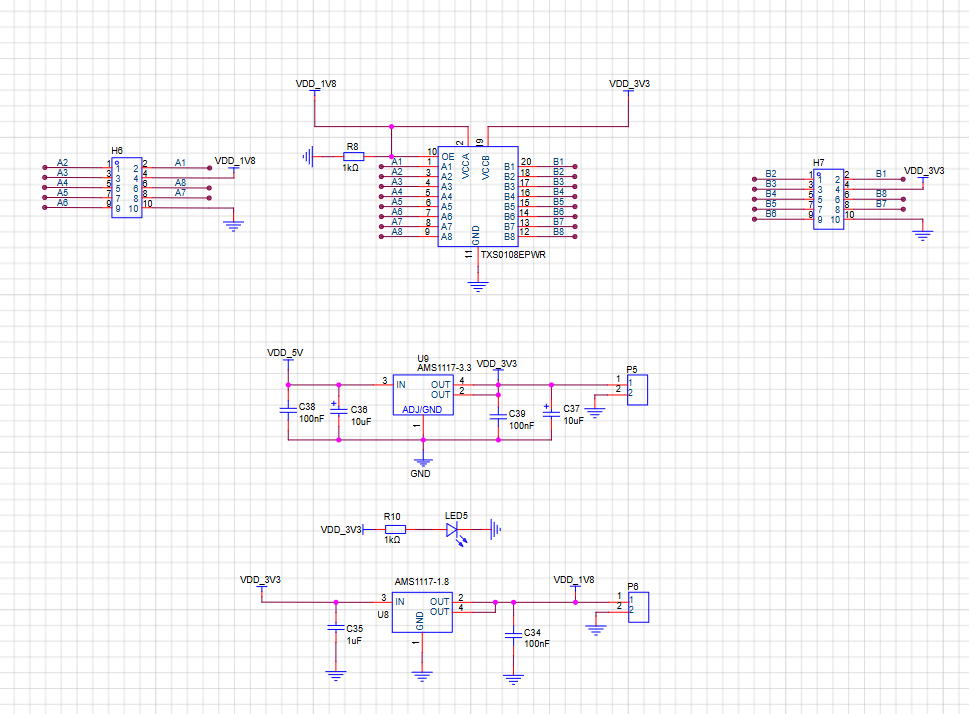

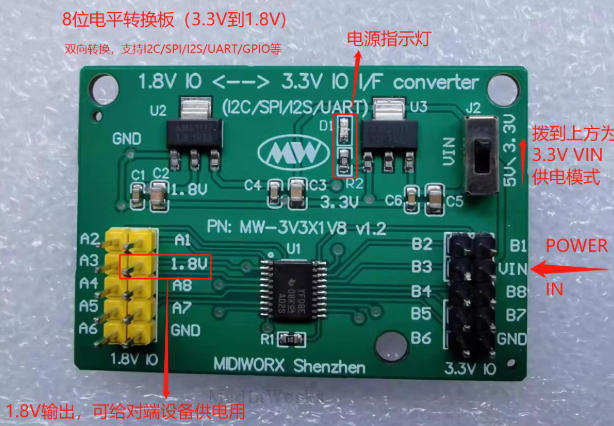

3.3V-1.8V电平转换测试、以TXS0108E、NPN,NMOS方案为例

上述两个模块都测试过,测试结果相似。信号发生器产生3.3Vpp/10K Hz 方波测试1.8V信号输出结果模块出现顶部失真,原因是因为电平转换芯片需要转换的正电压,转换的方波如果没有设置偏置,会导致信号源的方波电平小于电平转换的所需的触发电平导致波形顶部失真。偏置设置为1.65V输出波形正常。但是模块接上负载后波形又出现顶部失真!!!TXS0108采用弱上拉设计(内部约4 kΩ上拉电阻),其驱动能

TXS0108双向电平转换芯片

上述两个模块都测试过,测试结果相似。

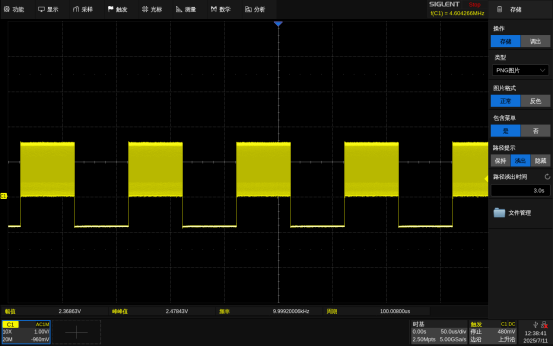

信号发生器产生3.3Vpp/10K Hz 方波

测试1.8V信号输出结果

模块出现顶部失真,原因是因为电平转换芯片需要转换的正电压,转换的方波如果没有设置偏置,会导致信号源的方波电平小于电平转换的所需的触发电平导致波形顶部失真。偏置设置为1.65V输出波形正常。

但是模块接上负载后波形又出现顶部失真!!!

原因分析:

-

输出驱动能力与内部结构限制

TXS0108采用弱上拉设计(内部约4 kΩ上拉电阻),其驱动能力类似开漏输出,依赖外部负载完成电平转换。在低频时,方波高电平持续时间较长(10 kHz周期为100 μs),弱上拉无法持续维持高电平电压,导致电压缓慢下降(顶部失真)。而高频时(10 MHz周期为0.1 μs),高电平持续时间极短,电容来不及放电,因此波形更接近方波。 -

容性负载的影响

-

探头电容与寄生电容:示波器探头在X1挡位输入电容较大(约47–110 pF),在低频时会与芯片内部上拉电阻形成RC电路,导致高电平按指数曲线衰减(顶部失真)。高频时电容阻抗(𝑍𝑐=1/(2𝜋𝑓𝐶)Zc=1/(2πfC))降低,影响减弱。

-

走线寄生电容:PCB长走线或飞线引入的寄生电容(通常10–50 pF)会加剧RC效应,进一步拉低高电平。

-

-

使能引脚(OE)配置问题

OE引脚需接VCCA(低压侧电源),若错误接VCCB(高压侧),可能导致内部电路工作异常。此外,上电时OE未保持低电平(待电源稳定后再拉高),可能造成输出状态不稳定。 -

芯片适用场景差异

TXS0108适合开漏总线(如I²C),对推挽信号(如SPI、方波)驱动能力不足。高频时因信号跳变快,内部One-shot电路(加速边沿的脉冲发生器)能部分补偿驱动,而低频时此机制无效。

尝试办法:输出加串联电阻以及输出引脚加上上拉电阻,没啥效果。

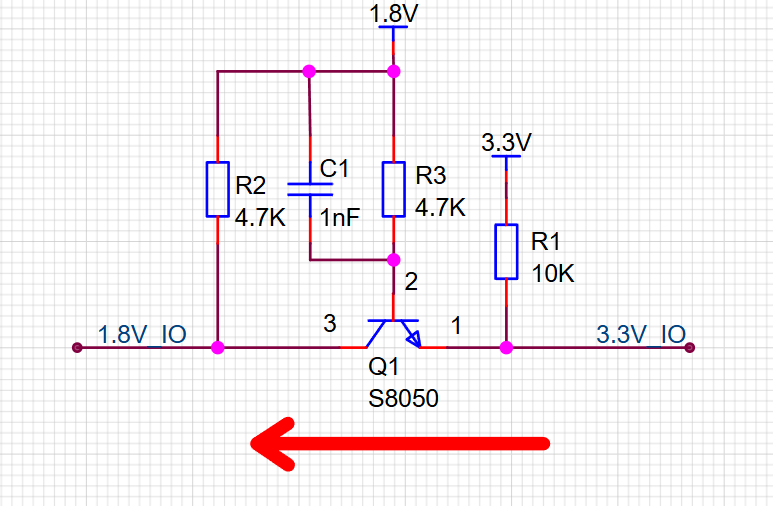

NPN电平转换电路

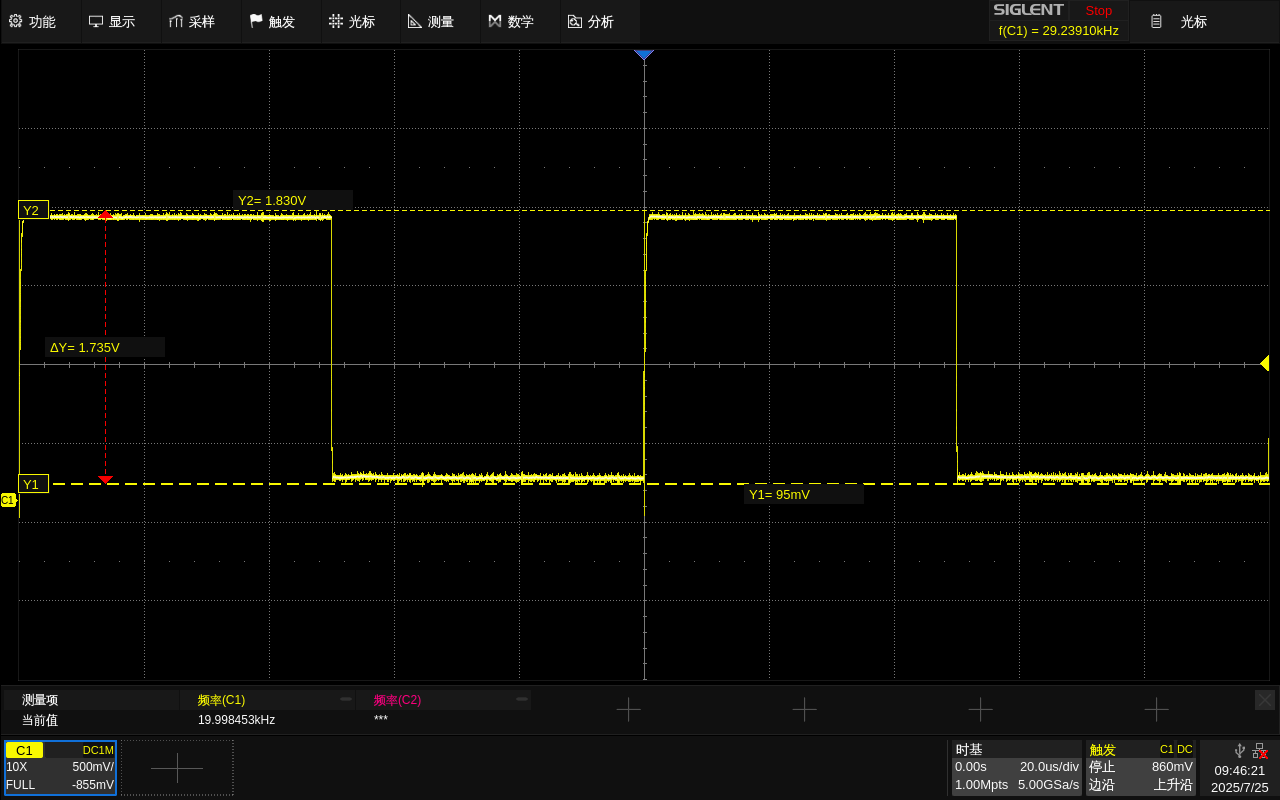

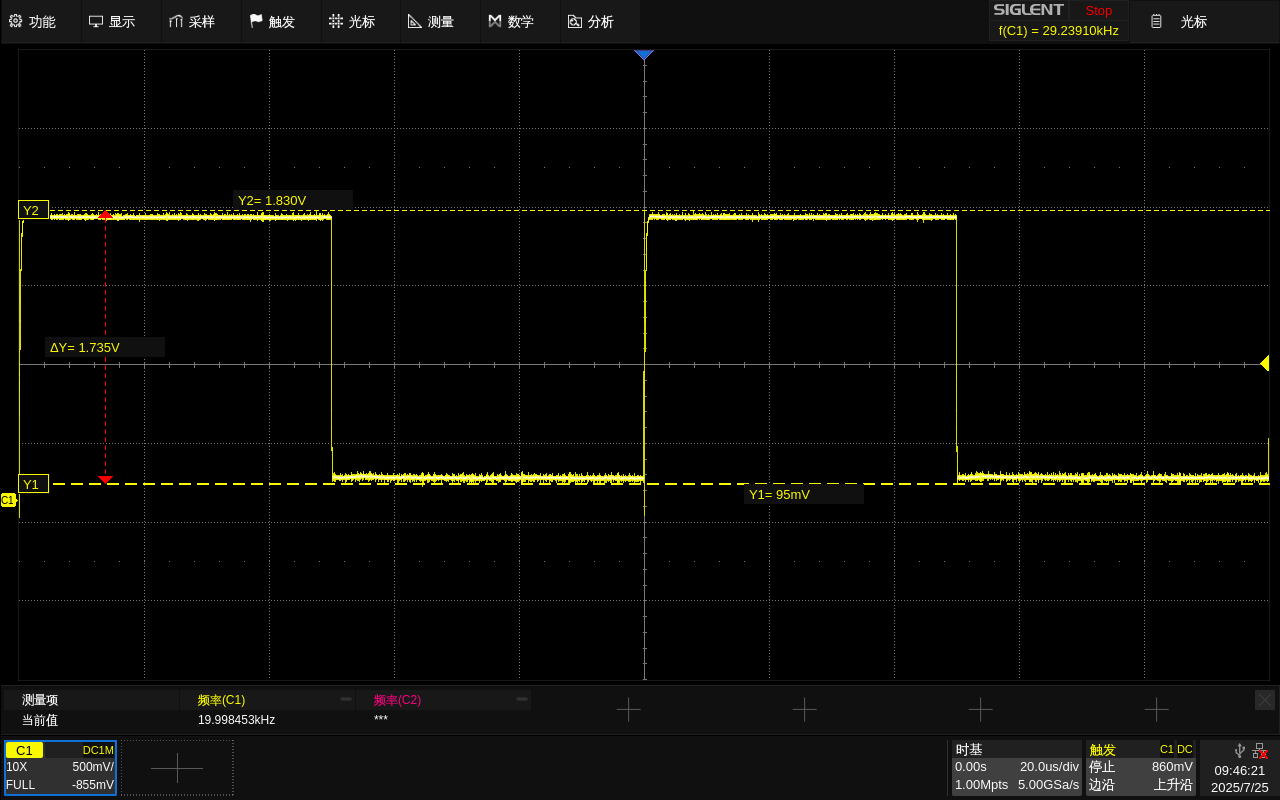

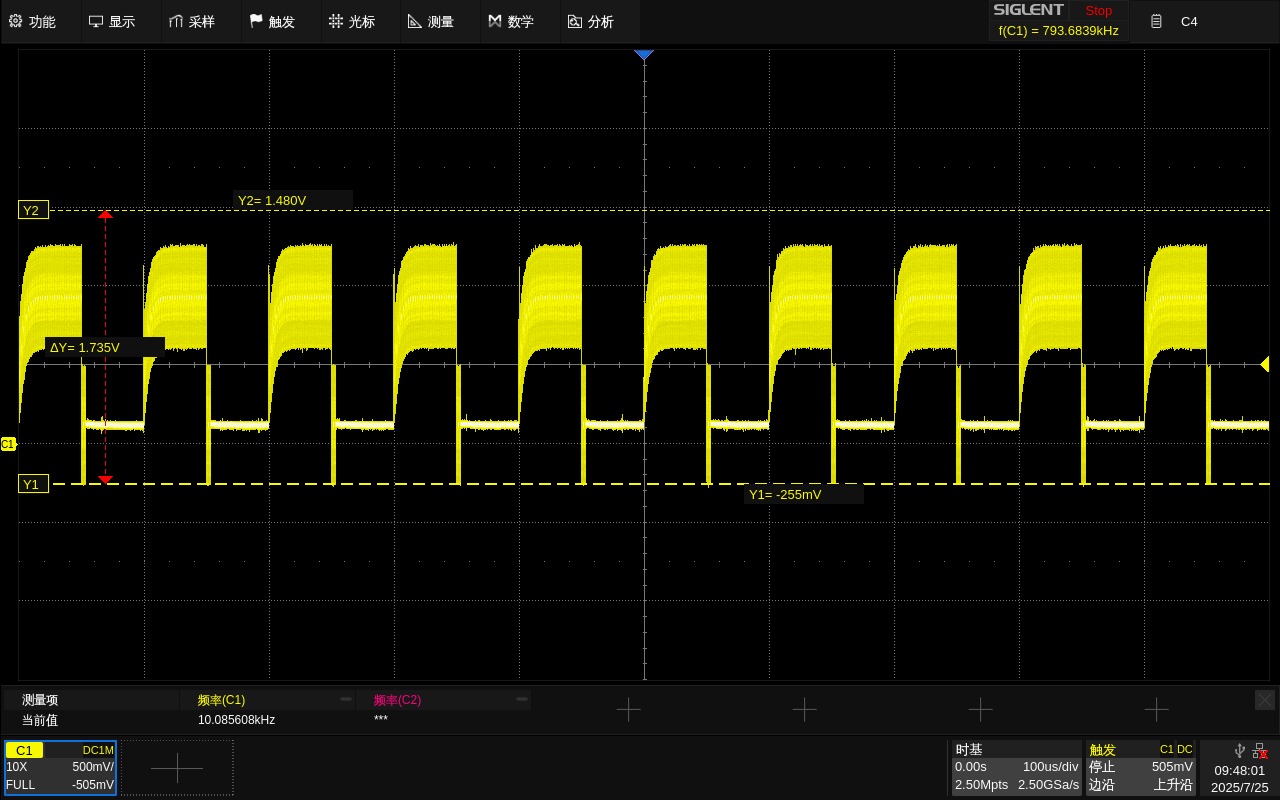

信号发生器产生3.3Vpp/10K Hz 方波,偏置1.65V

不加负载测试结果

加上负载测试结果

原因分析:

-

三极管开关速度限制:

-

当三极管从饱和导通状态切换到截止状态时,基区存储电荷需要释放,导致关断延迟。

-

基极电阻过大时,电荷释放速度变慢,加剧了上升沿的缓慢爬升和振荡。

-

-

负载电容效应:

-

负载端输入电容(如MOS栅极电容、走线寄生电容)与集电极电阻形成RC电路。

-

三极管关断后,电容通过集电极电阻充电,导致上升时间变长,易受干扰。

-

-

密勒效应:

-

三极管集电极-基极间电容在开关瞬间产生反馈,加剧波形失真。

-

-

电路布局问题:

-

长走线引入电感,与负载电容形成LC谐振,导致振铃(高频振荡)。

-

尝试方法:输出加串联电阻或加RC滤波,没啥效果。

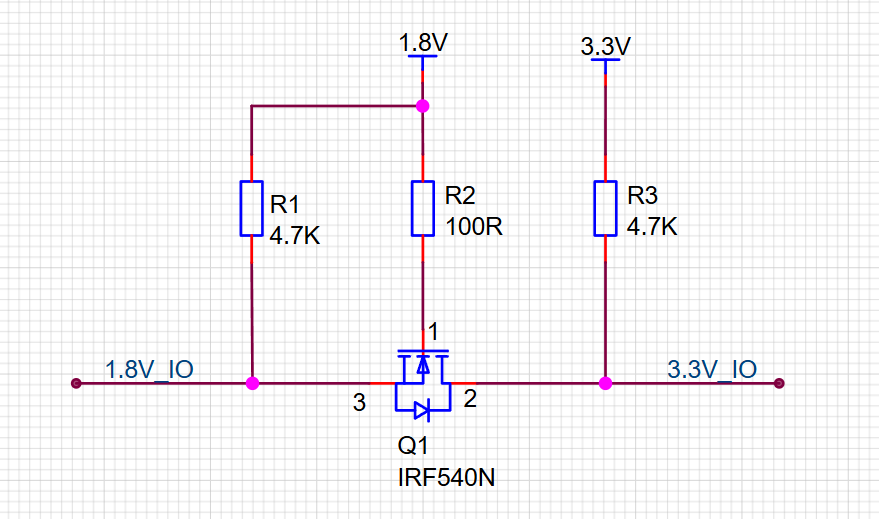

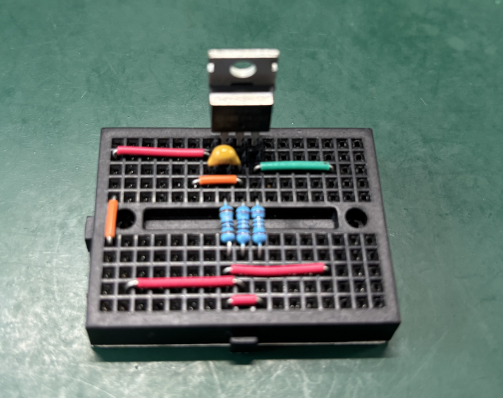

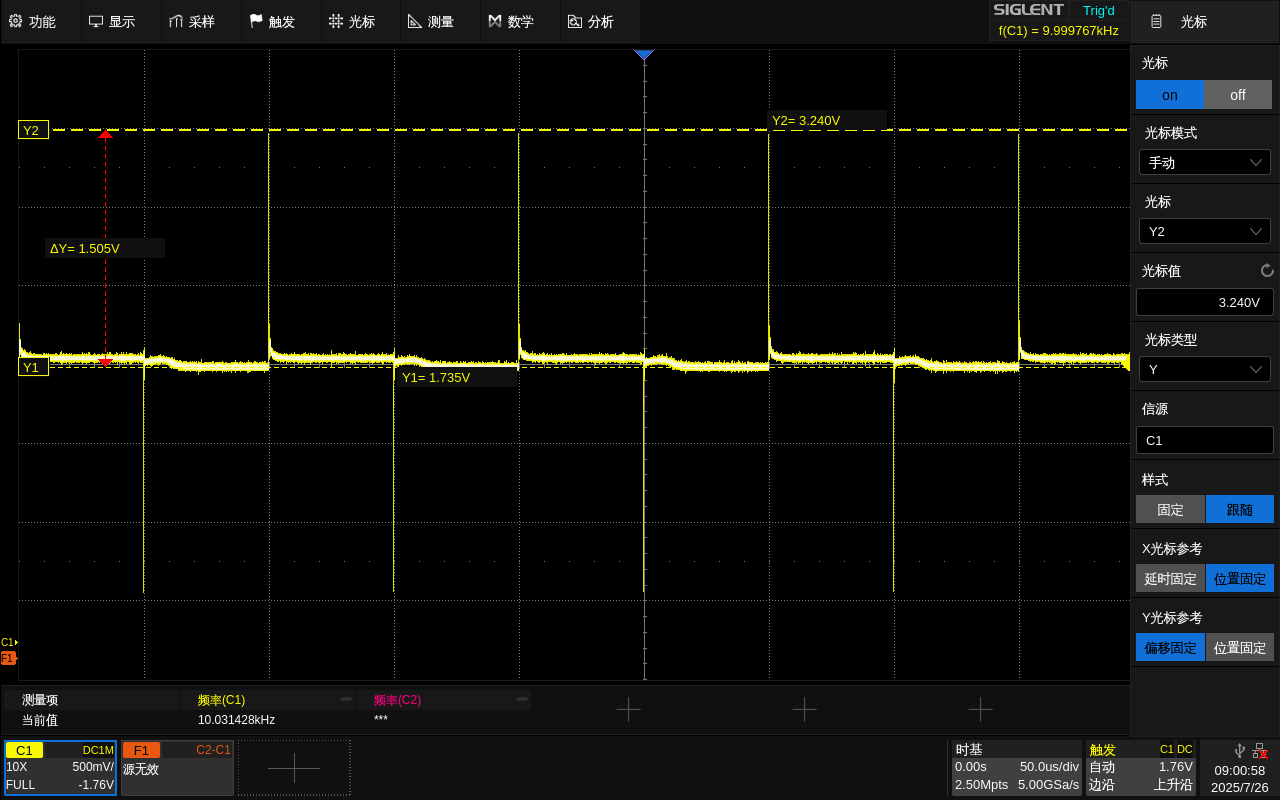

NMOS电平转换电路

信号发生器产生3.3Vpp/10K Hz 方波

核心原因分析(为什么高电平被“吃掉”只剩突刺)

-

上拉能力严重不足 + 负载电容过大

-

当NMOS关断时,上拉电阻太弱,无法在短时间内将负载电容充电到1.8V。

-

结果:高电平还未建立完成,下一个周期NMOS又导通了(将输出拉低),示波器上只看到一个短暂“突起”。

-

-

负载存在动态电流(如逻辑门翻转)

-

负载在需要高电平时突然吸入大电流(如CMOS输入电容充电),而上拉电阻无法提供足够电流,导致电压瞬间崩溃。

-

-

NMOS未完全关断(栅极问题)

-

栅极控制信号的高电平不足(如3.3V信号被衰减),导致NMOS工作在线性区,相当于一个电阻下拉输出。

-

-

信号频率过高

-

方波周期太短,高电平时间小于电路建立稳定电压所需时间(RC延时)。

-

尝试办法:大幅度减小上拉电阻的阻值或将栅极上的电阻改为0欧,没啥效果。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)