数字IC后端培训教程系列之PR Innovus工具写出Calibre LVS用的Netlist详细步骤

数字IC后端培训教程系列之PR Innovus工具写出Calibre LVS用的Netlist详细步骤

在数字IC后端设计实现chipfinish阶段需要写出很多数据,比如netlist,def,gds,lib和lef等文件。

今天给大家分享PR工具Innovus写出Calibre物理验证LVS要用的netlist的详细步骤。

1)derive pg

确保所有cell(包括physical only cell)的derive pg都是正确的。

globalNetConnect VDD_CORE -type pgpin -pin {VDD} -inst * -override

globalNetConnect VSS -type pgpin -pin {VSS} -inst * -override

PG逻辑连接的脚本编写需要建立在对设计powerplan结构理解的基础上。这个是过Calibre LVS的基石。

比如咱们社区T12nm A55项目,如果使用如下的globalNetConnect脚本,则会出现问题。VPP和VBB分别是nwell和psub的接触点,其中PD_PSO是需要power down的domain,而PD_AW_ON是常开的domain。

globalNetConnect VDD_LOCAL -type pgpin -pin {VPP} -inst * -powerDomain PD_PSO

globalNetConnect VDD_CORE -type pgpin -pin {VPP} -inst * -powerDomain PD_AW_ON

globalNetConnect VSS -type pgpin -pin {VBB} -inst * -powerDomain PD_PSO

globalNetConnect VSS -type pgpin -pin {VBB} -inst * -powerDomain PD_AW_ON

2)删除空module

deleteEmptyModule

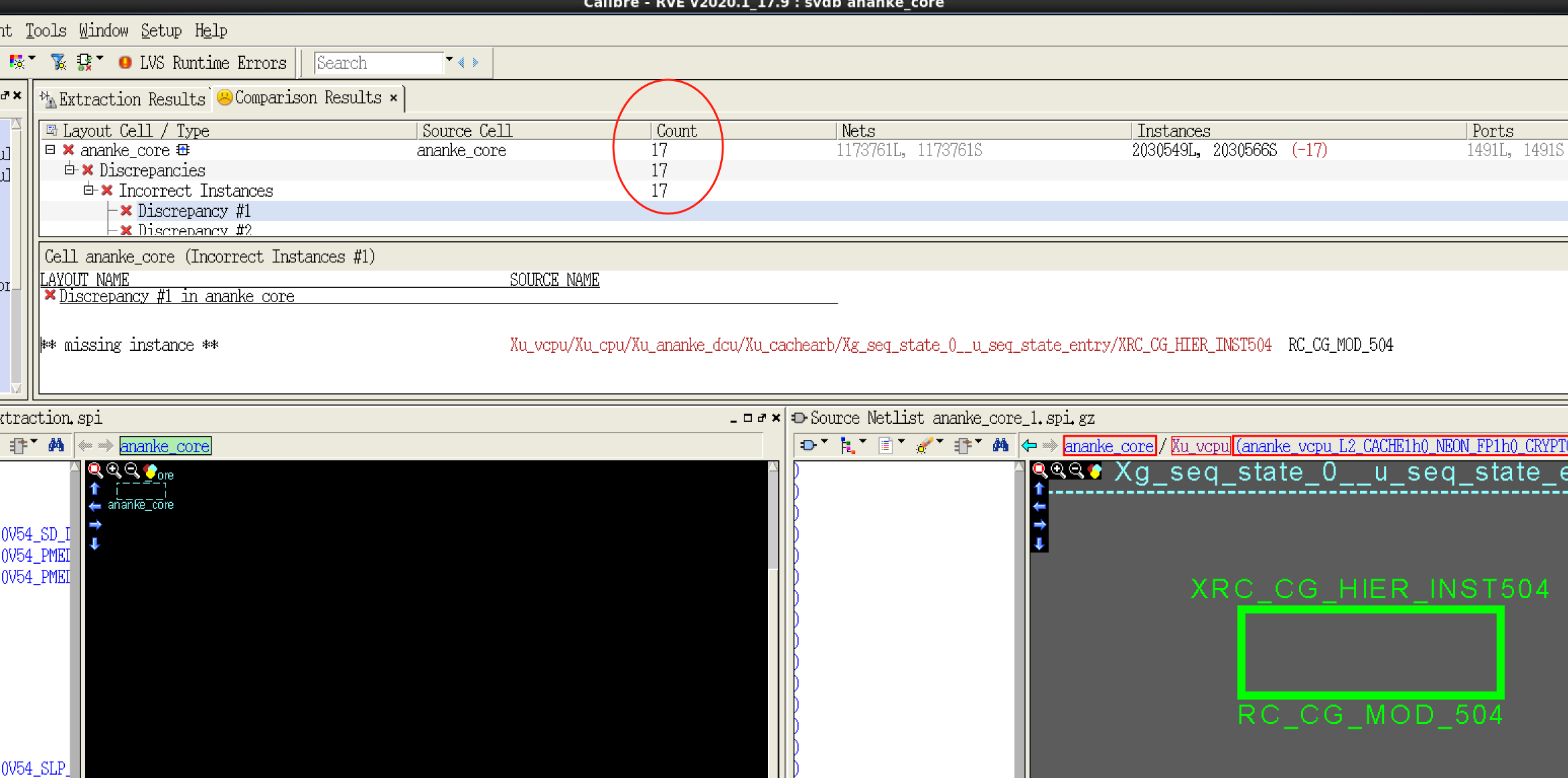

如果设计中存在空module,在做calibre LVS检查时会报Incorrect Instances的错误,具体见如下图所示。

咱们社区也分享过一个实际后端项目案例,设计中存在几个空module。小编也手把手教大家如何进行LVS问题debug,并解决这样的Calibre LVS问题。感兴趣的可以在社区通过搜索关键词“delete”,即可快速找到这份教程。

物理验证Calibre LVS Stamping Conflict SoftConnect案例解析

3)physical only cell处理

对于有device的physical only cell,我们必须在写netlist时通过incldePhysicalCell选项把它们写出来,否则会出现layout gds和source netlist 不匹配的情况。

saveNetlist …/data/cortexa7_lvs.vg

-includePhysicalCell {DCAP32BWP40P140 DCAP16BWP40P140 DCAP8BWP40P140}

-excludeLeafCell

-includePowerGround

-flattenBus

4)Split Bus处理

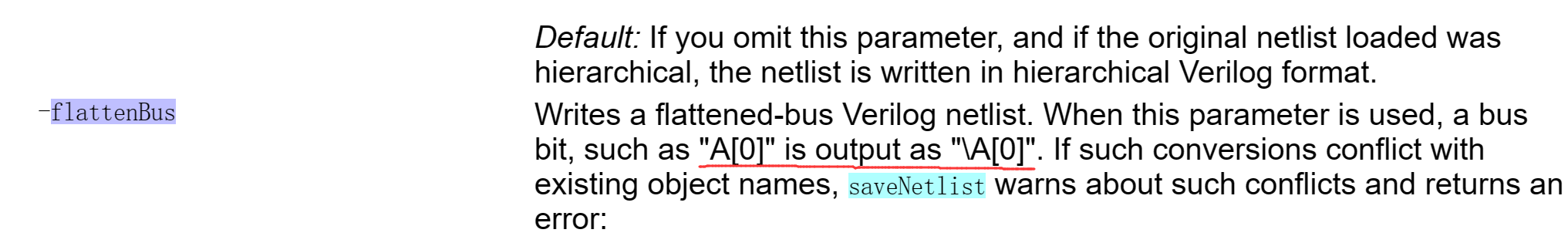

如果Design里面有Macro,比如SRAM,在SRAM的.spi网表中所有的pin都是单个bit声明的,那么在导出网表的时候我们必须把Bus来flatten成单个的bit,加上选项-flattenBus即可,否则在做完v2lvs之后做LVS的时候会报这些bus和pin不匹配的问题。

更多推荐

已为社区贡献51条内容

已为社区贡献51条内容

所有评论(0)