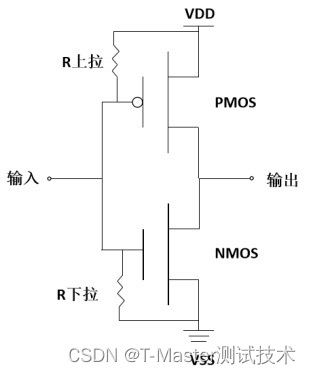

leakage漏电流:测试遇到有上、下拉电阻的漏电流是怎样的?

芯片漏电流测试时,通常判定值为-10uA~10uA,正常测试值一般均在该范围内,但有时会发现测试值超过判定值的现象,当出现漏电流超过判定值时,可以查看产品手册或询问设计人员,芯片引脚是否有上、下 拉电阻设计。在芯片设计时,为了使芯片引脚状态处于更稳定状态,对于一些引脚高低电平状态对芯片工作影响大的引脚,会采用上、下拉电阻设计,以防止芯片上电时引脚处于不定态,从而造成芯片进入一些非期望状态。如复信号

芯片漏电流测试时,通常判定值为-10uA~10uA,正常测试值一般均在该范围内,但有时会发现测试值超过判定值的现象,当出现漏电流超过判定值时,可以查看产品手册或询问设计人员,芯片引脚是否有上、下 拉电阻设计。

在芯片设计时,为了使芯片引脚状态处于更稳定状态,对于一些引脚高低电平状态对芯片工作影响大的引脚,会采用上、下拉电阻设计,以防止芯片上电时引脚处于不定态,从而造成芯片进入一些非期望状态。

如复信号,低电平0为有效信号,那么就会设计一上拉电阻到VDD端,这样在外部输入VIL前,均处理无效的高电平1的状态。又如一些使能信号,高电平1有效,那么就会设计一下拉电阻到VSS地端,这样在外部输入VIH前,均处理无效的低电平0的状态。那么,如果引脚有上、下拉电阻,会对漏电流测试有什么影响?看下图两个信号的漏电流测试:

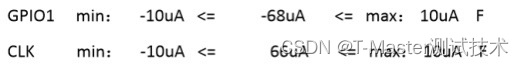

上图为GPIO1和CLK的漏电流测试,GPIO1漏电流为-68uA,CLK漏电流为66uA。

首先看GPIO1,漏电流为负值,由芯片VDD端流向输入栅级端则为负,因此可判定为IIL测试,可以看到测试到的漏电流为-68uA,那么说明GPIO1引脚有一上拉电阻设计,我们可以通过欧姆定律初步计算上拉电阻的阻值:

R=U/I=1.8(V)/68(uA)=26.47K(Ω)

则说明GPIO1引脚上有一约26.47K的上拉电阻。

再看CLK,漏电流为正值,由芯片输入栅级端流向VSS地端则为正,因此可判定为IIH测试,可以看到测试到的漏电流为66uA,那么说CLK引脚有一下拉电阻设计,我们可以通过欧姆定律初步计算上拉电阻的阻值:

R=U/I=1.8(V)/66(uA)=27.27K(Ω)

注:上述测试电源电压为1.8V

则说明CLK引脚上有一约27.77K的下拉电阻。

对于这种有上、下拉电阻的引脚漏电流测试,可以根据需求进行测试设计,若不需要测试这些引脚,那么测试引脚不加入即可。若需要测试这些引脚,可以将正常引脚放入一个测试项,另外值接近的放为一测试项,这样就可以分别设定判定值完成漏电流的测试。

更多推荐

已为社区贡献7条内容

已为社区贡献7条内容

所有评论(0)