数字IC后端实现TOP Floorplan专家秘籍

数字IC后端实现TOP Floorplan专家秘籍2020 年是不平凡的一年,新冠疫情战役也还未结束。目前这场战役已经进入关键时期,希望各自继续做好自身防护,少出门,少聚餐,继续在家办公,这样也算是为社会做点小贡献。各位都知道,小编之前都是周末泡在咖啡厅码字的,这个时候也不敢出门,所以只能趁娃睡觉时间来码字了。今天想跟大家分享数字 IC 后端实现中关于 top floorplan 规划的相关内容。

数字IC后端实现TOP Floorplan专家秘籍

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

2020 年是不平凡的一年,新冠疫情战役也还未结束。目前这场战役已经进入关键时期,希望各自继续做好自身防护,少出门,少聚餐,继续在家办公,这样也算是为社会做点小贡献。

各位都知道,小编之前都是周末泡在咖啡厅码字的,这个时候也不敢出门,所以只能趁娃睡觉时间来码字了。今天想跟大家分享数字 IC 后端实现中关于 top floorplan 规划的相关内容。

Die Size 确定

我们知道,一个 chip 的形状要么是长方形,要么是正方形,因此芯片的尺寸取决于它的长和宽的大小。对于相同大小的芯片,可以做成方形的,可以做成瘦高型,也可以做成矮胖型。至于做成哪种类型的,绝对不是看心情,随意拍板的。这个过程涉及到 IO Ring,IP 的位置和绕线资源的估算。

思考题: 对于一个工艺,如果横向绕线资源不够的设计实现,请问应该选用哪种类型的形状?

现在的 SOC 设计,大都是 hierarchical 的设计实现方式。因此芯片中的子模块面积,IP 面积,memory 面积,IO Ring 面积和各种 channel 的面积直接决定了芯片的大小。

对于一个 IO/PAD Limitted 的芯片,它的面积受限于 IO/PAD 的数量。因为芯片中 IO 的数量太多,导致芯片的长宽拉的比较大。对于这种情况,可以考虑对IO 进行精简,比如去掉一些不太重要的 IO 或对 IO 进行复用等。

对于一个 CORE Limitted 的芯片,它的面积受限于芯片中各个子模块的面积大小。对于这种情况,各个子模块的数字后端实现就必须加大火力进行抠面积,将利用率最到最高,从而将芯片做小。

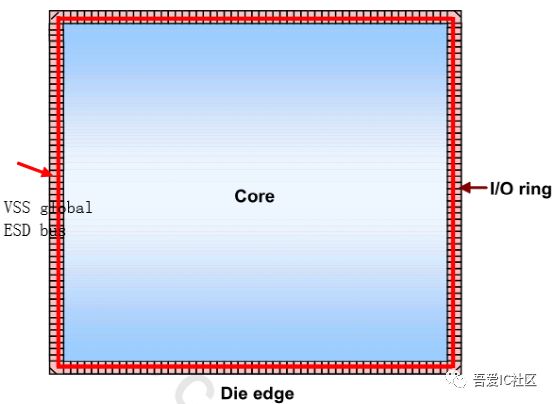

IO Ring 的设计

IO Ring 的设计会直接影响芯片的面积大小。因此,小编觉得有必要单独拿出来做一个介绍。

- Power/Ground CELL 添加

大部分情况下,前端集成设计时只会例化 GPIO,并不会例化 physical only 的 cell,比如 power&ground cell。因此,拿到前端提供的 netlist,首先要确定添加 PG CELL 的数量。

这里涉及到给 core 供电的 power/ground cell 和给 IO 供电的 power/ground cell。前者要根据芯片的Total power来估算需要的 power/ground cell 数量。后者则需要根据各个 IO Domain 的 IO 数量来计算SSO(Simultaneously Switching Output),最终确定对应的 power/ground cell 数量。

关于 SSO 的详细计算,请移步小编的知识星球,小编之前在星球上分享了一份非常详细的文档。

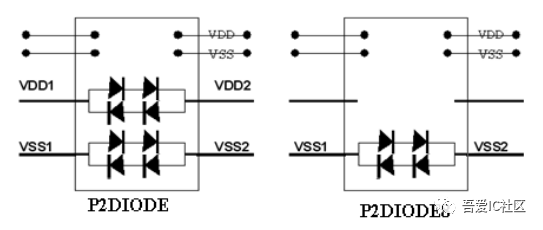

- Power Cut 等 cell 添加

除了添加 power/ground cell 外,还需要根据 vendor 要求添加一系列的physical only的 cell,比如 power cut cell,power on controll cell,corner cell 等。以 power cut cell 为例,一般在两个不同 IO domain 之间需要添加这类 cell。

大部分 foundary 会提供几种不同类型的power cut cell,每种结构稍有不同,有的类型是 Noise 隔离好一点,有的类型是 ESD 保护会强一些。这个需要根据设计应用需求,进行抉择。

IO Placement

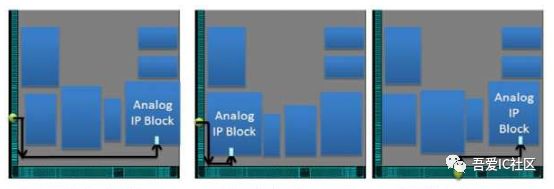

IO 的摆放需要根据硬件 PCB 的布局来摆放。对于高速接口的 IO,它的摆放位置显得更加重要。

以上图最左侧示例,如果黄色部分 IO 属于高速接口的 IO,那么它与 Analog IP 的 path 的时序一定有问题。

如果前期的 IO placement 是按照最左侧图示摆放,没有意识到接口时序问题,那么后期改动会非常大,基本上等于整个芯片(包括 block)的实现都要重新来一遍。

如果前期能够意识到这个风险,那么完全可以将黄色的 IO 摆放在最下边那条边的中间位置。当然如果硬件 PCB 允许的情况下,还可以将 Analog IP 挪到最左侧。

IP 摆放

IP 摆放需要遵循以下原则:

- 符合时钟 / 数据流走向

比如 PLL 的摆放,需要靠近 destination,使得时钟路径最短。

- Poly Orientation

对于 28nm 甚至更先进工艺节点,摆放 IP 时需要特别注意 POLY 方向问题。因此在这样的工艺节点,是不允许 90 度翻转的。一旦方位出错,后期的 floorplan 就需要全面改一遍,项目的 schedule 就完全不受控制。

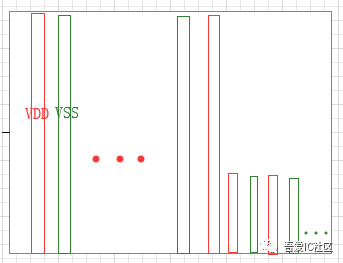

- IR Drop Aware 摆放法

有些 IP 内部抽出来的 PG PIN, 分布比较不好,如下图所示。如果该 IP 这样摆放,而且 top powerplan 用的最高层也是众向的 layer,那么这个 IP 的供电将是个大问题。

如果 IP 能做 90 翻转,那也可以解决 IR Drop 的问题。如果不能翻转,那么就需要调整 top powerplan 的规划。因此,摆放 IP 的时候也要充分考虑 IP 供电问题,否则性能可能完全达不到预期。

数字 IC 设计后端实现前期预防 IR Drop 的方法汇总

Top Partition

TOP Partition 主要包括子模块切分和pin assignment。这部分内容之前已经分享过,可以查阅这篇文章。

【机密】从此没有难做的 floorplan(数字后端设计实现 floorplan 篇)

今天再额外分享两个比较实用的技术经验。

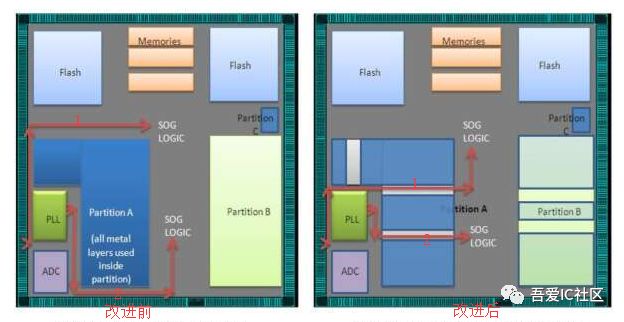

以下图设计为例,路径 1 和路径 2 受 Partition A 的限制,只能走比较远的路径(模块 A 身上有 route blockage)。这种情况下,timing 可能无法 meet 设计需求。那么,我们可以在模块 A 中预留一部分 route 资源给这部分走线,改进后的效果图如下图右侧图所示。

如果模块 A 的宽度很宽,能否这么处理呢?为什么?这个留给大家思考。

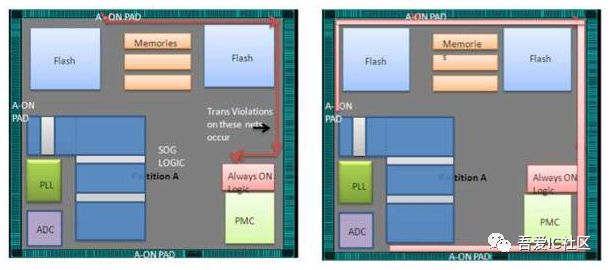

另外一个案例就是如果一个 AON Pad 要跨一个 power domain,最终到达 Always ON logic,如下图所示。由于它们之间的距离比较远,如果直接飞,不经过任何的 buffer,一定会有 max transition 的问题。那么怎么解决呢?为了修 max transition violation,只能插 buffer,这里可以做一路 buffer tree。需要注意的是,这里的 buffer 必须是 AON 的 buffer。同时还得为这些 AON buffer 供好电。

基于上述分析,我们可以尝试单独做一个模块,用来走 AON PAD 到 Always ON 的走线,模块内部的逻辑只有 buffer。

好了,今天的内容分享就到这里。如果你喜欢小编的文章,帮忙点下**“在看”**并转发给你的朋友,算是鼓励支持下小编呗。

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 ****):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

-

定期将项目中碰到的问题以案例的形式做技术分享

吾爱 IC 社区知识星球星主为公众号” 吾爱 IC 社区” 号主,从事数字 ic 后端设计实现工作近八年,拥有55nm,40nm,28nm,22nm,14nm等先进工艺节点成功流片经验,成功tapeout 过三十多颗芯片。

这里是一个数字 IC 设计实现高度垂直细分领域的知识社群,是数字 IC 设计实现领域中最大,最高端的知识交流和分享的社区,这里聚集了无数数字 ic 前端设计,后端实现,模拟 layout 工程师们。

在这里大家可以多建立连接,多交流,多拓展人脉圈,甚至可以组织线下活动。在这里你可以就数字 ic 后端设计实现领域的相关问题进行提问,也可以就职业发展规划问题进行咨询,也可以把困扰你的问题拿出来一起讨论交流。对于提问的问题尽量做到有问必答,如遇到不懂的,也会通过查阅资料或者请教专家来解答问题。在这里鼓励大家积极发表主题,提问,从而促进整个知识社群的良性循环。每个月小编会针对活跃用户进行打赏。

最重要的是在这里,能够借助这个知识社群,短期内实现年薪百万的梦想!不管你信不信,反正已经进来的朋友肯定是相信的!相遇是一种缘分,相识更是一种难能可贵的情分!如若有缘你我一定会相遇相识!知识星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有438位星球成员,感谢这438**** 位童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。

欢迎关注 “吾爱 IC 社区”

微信号:ic-backend2018

点击 “阅读原文” 访问小编知识星球

更多推荐

已为社区贡献51条内容

已为社区贡献51条内容

所有评论(0)