嵌入式学习笔记11.9-GPIO_EMIO

但在生成HDL文件时,最顶层并没有引出emio引脚,所以综合也看不到,不懂这是为什么。选用了EMIO连接PL端的一个按键用于控制核心板上一个LED的亮灭。STEP4:生成顶层Bitstream文件并导出硬件。找不到EMIO的引脚!不是4改8的问题,我重新导出一下也有了。emio连接L14及PL按键key0。对比可见多了一个EMIO连接PL。STEP1:创建VIVADO工程。然后在导出硬件4改8就有

·

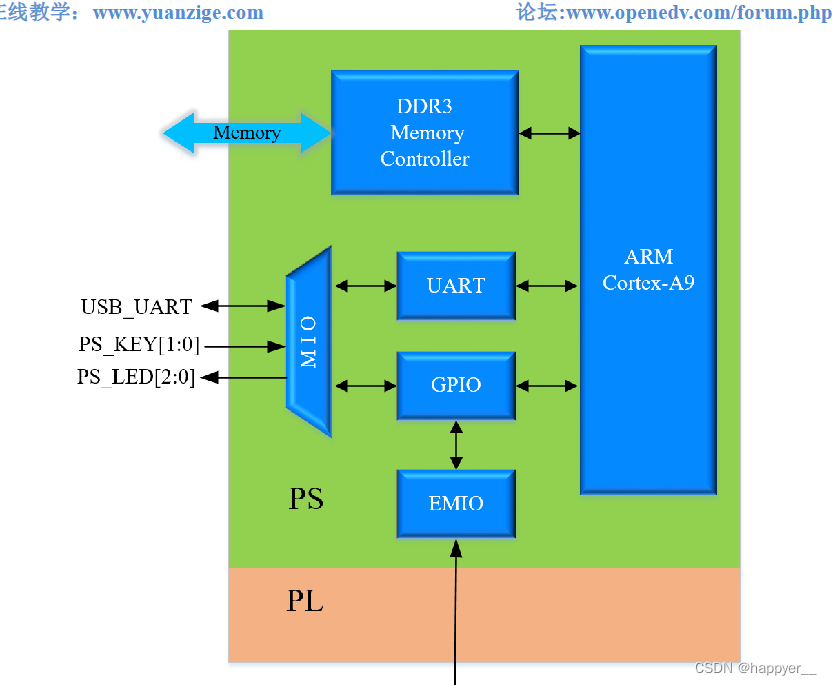

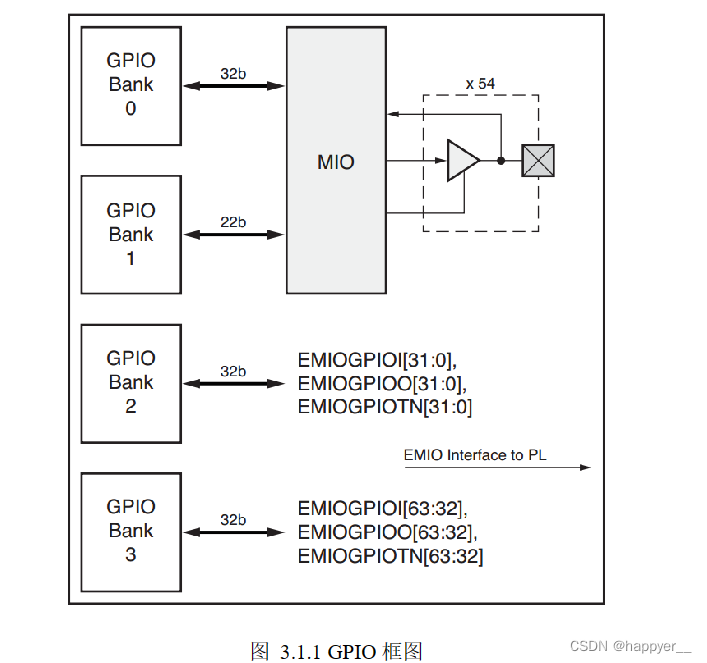

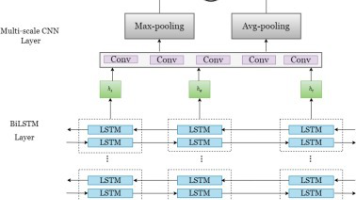

与前一个实验不同的地方:

选用了EMIO连接PL端的一个按键用于控制核心板上一个LED的亮灭

上图为本实验的系统框图

下图为上一个实验的系统框图

对比可见多了一个EMIO连接PL

在vivado硬件设置之中

STEP1:创建VIVADO工程

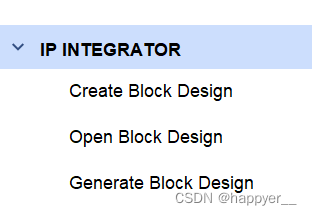

STEP2:使用IP Intergrator 创建Processing System

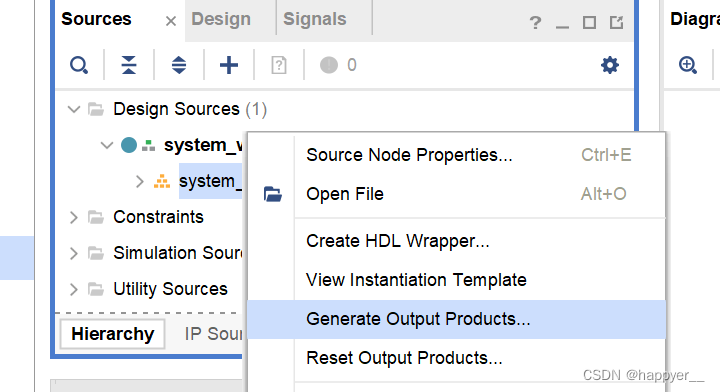

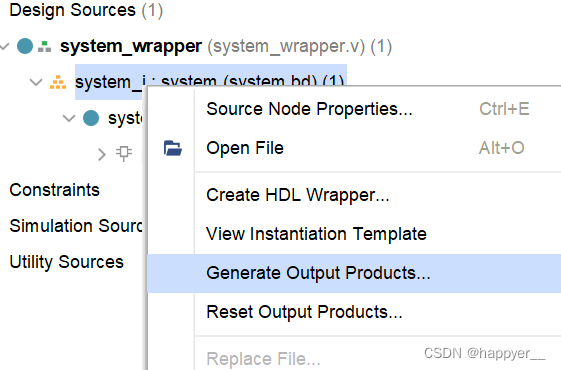

STEP3:生成顶层HDL

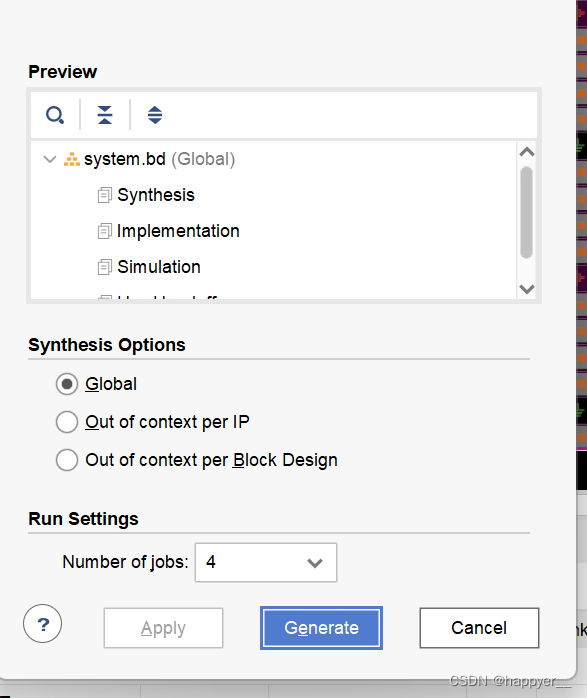

STEP4:生成顶层Bitstream文件并导出硬件

分配IO管脚

找不到EMIO的引脚!!!!!遇到问题

试了好一会

发现ip中有emio引脚

但在生成HDL文件时,最顶层并没有引出emio引脚,所以综合也看不到,不懂这是为什么

然后在导出硬件4改8就有了,

不是4改8的问题,我重新导出一下也有了

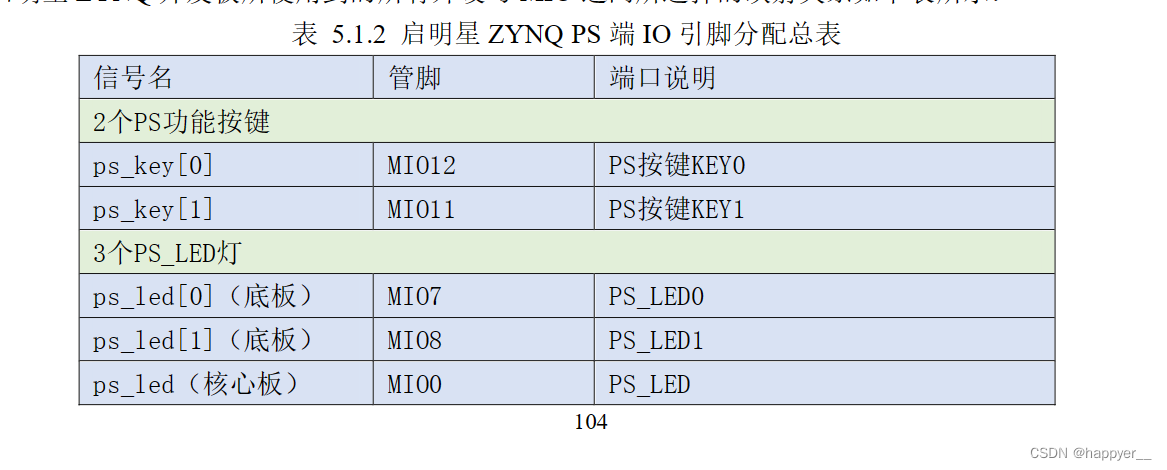

emio连接L14及PL按键key0

生成二进制文件

导出硬件(新建一个vitis文件夹)

打开vitis

step5:在vitis中新建工程

导入刚刚生成的xsa文件

新建源文件main.c

编写代码

Build project

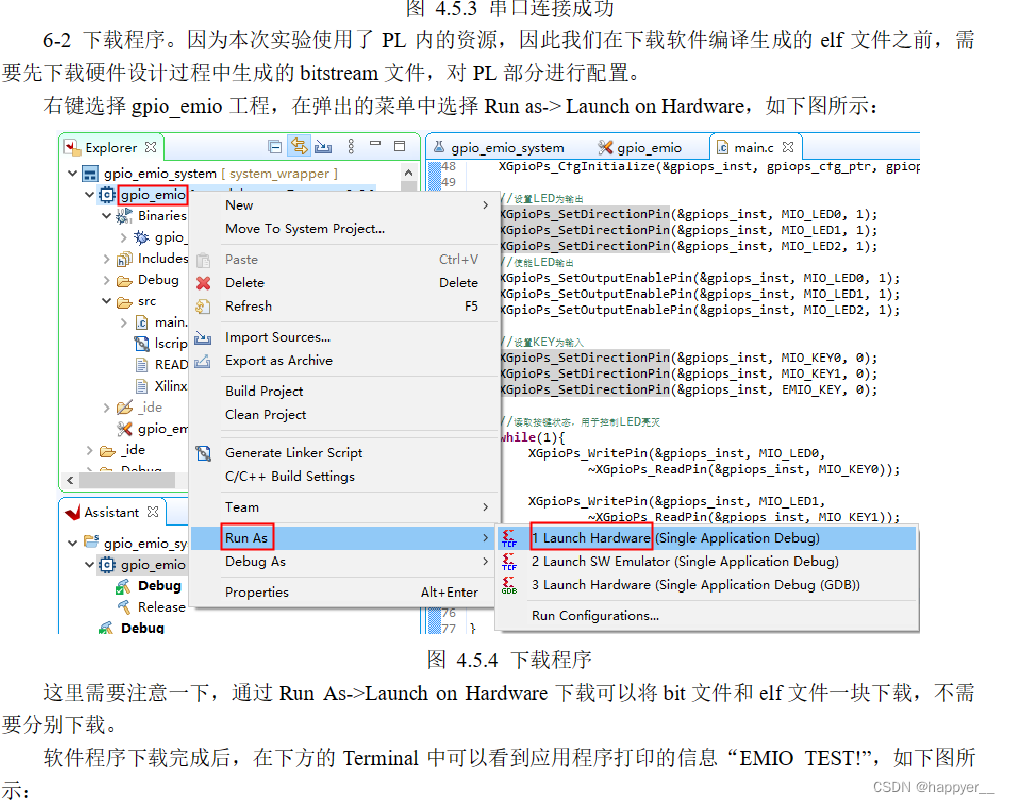

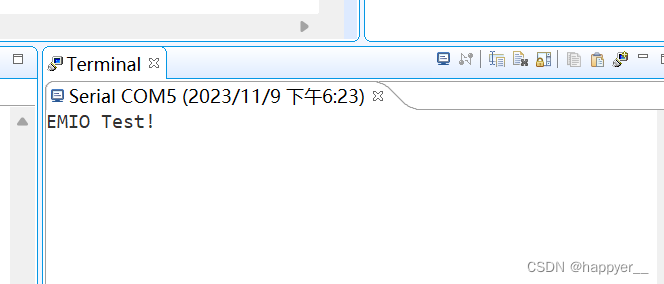

最后下载验证

1、设置串口

2、下载程序

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)