tmp1075温度传感器I2C数码管显示IIC温度verilog代码

tmp1075温度传感器I2C数码管显示IIC温度verilog代码(代码在文末付费下载)软件:ISE语言:Verilog代码功能: 使用verilog编写代码,读取IIC(I2C)接口的tmp1075温度传感器数据,并在数码管显示,代码兼容LM75 本代码已在Basys2开发板验证。else if (counter_div >= 10'd999)//分频产生50KHz频率,50M/50K=100

·

名称:tmp1075温度传感器I2C数码管显示IIC温度verilog代码(代码在文末付费下载)

软件:ISE

语言:Verilog

代码功能:

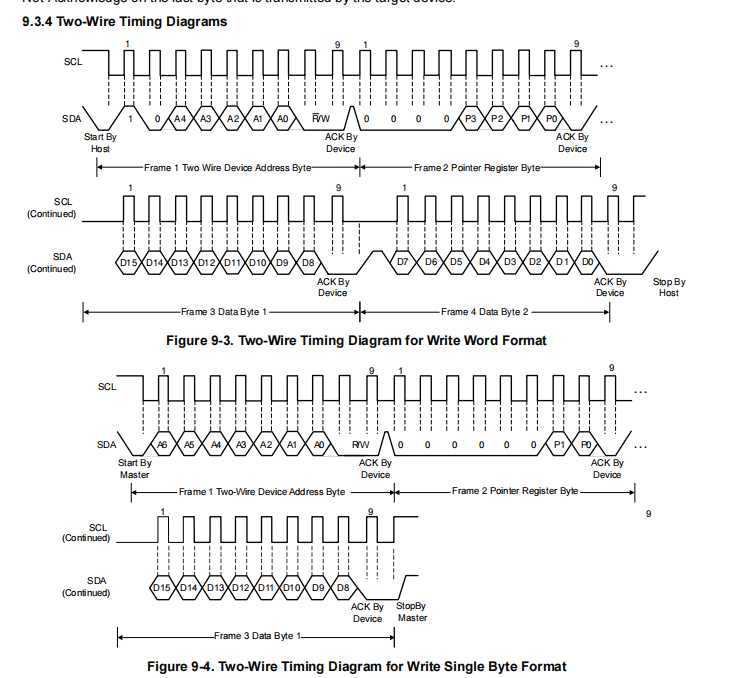

使用verilog编写代码,读取IIC(I2C)接口的tmp1075温度传感器数据,并在数码管显示,代码兼容LM75

本代码已在Basys2开发板验证,开发板资料:

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

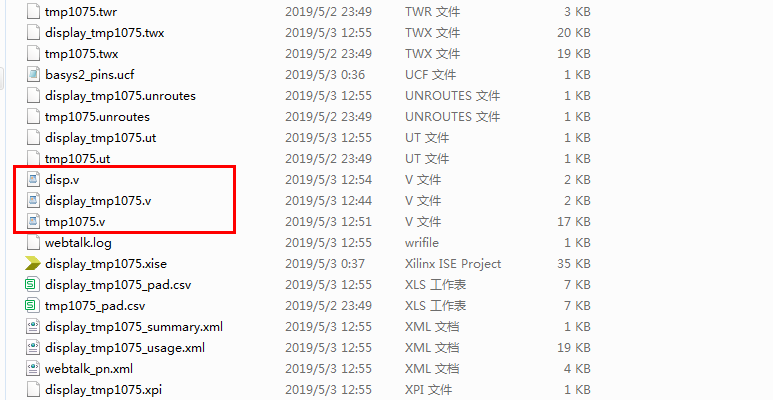

工程文件

部分代码展示

//tmp1075传感器IIC控制模块 module tmp1075_rd ( //input input sys_clk , input sys_rst_n , inout sda_port , //output output reg [10:0] tmp_out , output reg clk_sclk ); wire sda_in; //parameter define parameter WIDTH = 8; parameter SIZE = 8; //reg define reg [WIDTH-1:0] counter ; reg [9:0] counter_div ; reg clk_50k ; reg clk_200k ; reg sda ; reg enable ; reg [WIDTH-1:0] data_out ; reg [31:0] counter_init ; reg [10:0] buff ; //wire define wire [2:0] device_addr ; wire sda_input ; /******************************************************************************************************* ** Main Program ** ********************************************************************************************************/ //tmp1075 device address is 000, this value is no care ; assign device_addr = 3'b000;//地址000 // counter for gen a clk_50k : need count to 1000, for 50M/1000 = 50K hz always @(posedge sys_clk or negedge sys_rst_n) begin if (sys_rst_n ==1'b0) counter_div <= 10'b0; else if (counter_div >= 10'd999)//分频产生50KHz频率,50M/50K=1000=0~999 counter_div <= 10'b0; else counter_div <= counter_div + 10'b1; end // gen a clk_50k use counter_div : not use counter_div 0 - 500 is for i2c bus request start timing always @(posedge sys_clk or negedge sys_rst_n) begin if (sys_rst_n ==1'b0) clk_50k <= 10'b0; else if ((counter_div >= 375) && (counter_div < 875)) clk_50k <= 10'b1;//分频产生50KHz频率 else clk_50k <= 10'b0;//分频产生50KHz频率 end // counter for init for tmp1075 always @(posedge sys_clk or negedge sys_rst_n) begin if (sys_rst_n ==1'b0) counter_init <= 32'h0; else if ( counter_init < 32'h5f5e100 ) //十六进制5f5e100=100000000,50M计数100000000得2秒 counter_init <= counter_init + 32'b1; else ; end // gen a 200K CLK for work counter count always @(posedge sys_clk or negedge sys_rst_n) begin //产生200K频率用于counter计数 if (sys_rst_n ==1'b0) clk_200k <= 10'b0; else if ((counter_div >= 0 ) && (counter_div < 125)) clk_200k <= 10'b0; else if ((counter_div >= 125) && (counter_div < 250)) clk_200k <= 10'b1; else if ((counter_div >= 250) && (counter_div < 375)) clk_200k <= 10'b0; else if ((counter_div >= 375) && (counter_div < 500)) clk_200k <= 10'b1; else if ((counter_div >= 500) && (counter_div < 625)) clk_200k <= 10'b0; else if ((counter_div >= 625) && (counter_div < 750)) clk_200k <= 10'b1; else if ((counter_div >= 750) && (counter_div < 875)) clk_200k <= 10'b0; else if ((counter_div >= 875) && (counter_div < 1000)) clk_200k <= 10'b1; else ; end // when tmp1075 init finish, work counter start to add always @(posedge clk_200k or negedge sys_rst_n) begin if (sys_rst_n ==1'b0) counter <= 8'h0; else if ( counter_init == 32'h5f5e100 ) counter <= counter + 8'b1; //2s后counter开始以200K频率计数 else ; end //generate real clk for SCLK ,when the i2c bus is idle, make the clk wire high level always @(*) begin if ( counter >= 2 && counter <= 118 ) clk_sclk = clk_50k; else clk_sclk = 1'b1; end // output SDA data with tmp1075 data sheet request always @(*) begin //根据tmp1075数据手册要求,输出iic时序 case ( counter )

tmp1075相关资料:

更多推荐

已为社区贡献6条内容

已为社区贡献6条内容

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=224

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=224

所有评论(0)