**发散创新:NPU设计详解与实现**一、引言随着人工智能技术的飞速发展,神经网络处理器(NPU)的设计成为了研究热点。NPU

NPU作为专为神经网络运算优化的硬件平台,其设计涉及到硬件架构、算法优化、编译器设计等多个领域。本文将带您深入了解NPU设计的全过程,从概念到实现,为您呈现一个完整的NPU设计蓝图。本文详细阐述了NPU设计的全过程,从算法研究到实现与测试,为读者提供了一个完整的NPU设计蓝图。随着人工智能技术的不断发展,NPU将在更多领域得到应用,未来的研究方向包括进一步提高计算效率、降低功耗等。希望通过本文的阐

·

发散创新:NPU设计详解与实现

一、引言

随着人工智能技术的飞速发展,神经网络处理器(NPU)的设计成为了研究热点。NPU作为专为神经网络运算优化的硬件平台,其设计涉及到硬件架构、算法优化、编译器设计等多个领域。本文将带您深入了解NPU设计的全过程,从概念到实现,为您呈现一个完整的NPU设计蓝图。

二、NPU设计概述

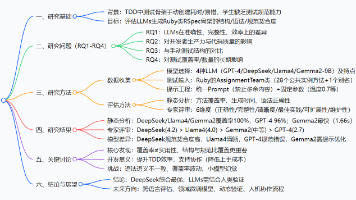

NPU设计主要包括以下几个关键部分:

- 神经网络算法研究:了解并研究各种神经网络算法,如卷积神经网络、循环神经网络等,为硬件实现提供理论基础。

-

- 硬件架构设计:根据神经网络算法的特性,设计高效的硬件架构,如计算单元、内存系统、控制单元等。

-

- 编译器优化:实现高效的软件编译工具,将高级语言编写的神经网络程序转化为硬件可执行的指令。

三、详细设计

- 编译器优化:实现高效的软件编译工具,将高级语言编写的神经网络程序转化为硬件可执行的指令。

1. 神经网络算法研究

-

卷积层设计:针对卷积层的特性,优化计算流程,提高计算效率。

-

- 激活函数处理:研究各种激活函数的性质,如ReLU、Sigmoid等,在硬件中实现时如何优化。

2. 硬件架构设计

(注:此处可以插入硬件架构的流程图或示意图)

- 激活函数处理:研究各种激活函数的性质,如ReLU、Sigmoid等,在硬件中实现时如何优化。

-

计算单元设计:根据神经网络计算的特点,设计高效的计算单元,如矩阵乘法器、累加器等。

-

- 内存系统设计:优化数据存取方式,提高数据访问速度,减少数据传输延迟。

-

- 控制单元设计:负责协调硬件各部分的工作,保证整个系统的稳定运行。

3. 编译器优化

(注:此处可以插入编译器优化流程图)

- 控制单元设计:负责协调硬件各部分的工作,保证整个系统的稳定运行。

-

指令集设计:根据硬件架构特点,设计一套高效的指令集。

-

- 代码优化策略:研究如何将高级语言编写的神经网络程序优化为硬件可执行代码。

-

- 性能分析与评估:通过模拟和实际测试,评估编译后的代码性能。

四、实现与测试

(注:此处可以插入实现与测试的流程图或截图)

- 性能分析与评估:通过模拟和实际测试,评估编译后的代码性能。

- 硬件实现:根据设计蓝图,实现硬件电路。

-

- 软件实现:编写驱动程序和测试程序。

-

- 联合测试:将软硬件结合起来进行测试,确保系统性能达到预期。

五、案例分析与性能评估

(注:此处可以插入实际案例的分析图或性能评估表)

- 联合测试:将软硬件结合起来进行测试,确保系统性能达到预期。

通过实际案例的分析和性能评估,验证NPU设计的有效性和优越性。

六、总结与展望

本文详细阐述了NPU设计的全过程,从算法研究到实现与测试,为读者提供了一个完整的NPU设计蓝图。随着人工智能技术的不断发展,NPU将在更多领域得到应用,未来的研究方向包括进一步提高计算效率、降低功耗等。希望通过本文的阐述,读者能对NPU设计有更深入的了解。

更多推荐

已为社区贡献14条内容

已为社区贡献14条内容

所有评论(0)