计算机硬件基础及嵌入式系统设计(精炼知识点)

该部分5分。

前言

该部分5分

知识点

计算机硬件基础

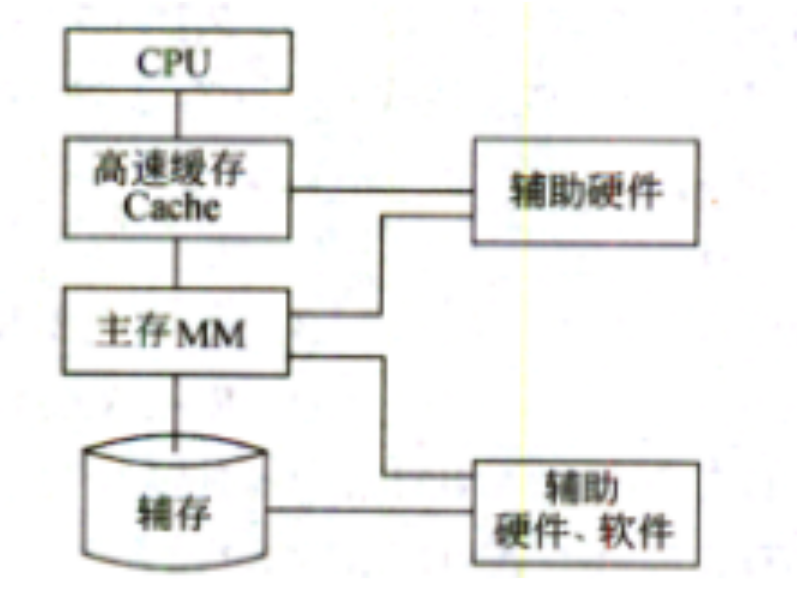

存储体系结构包括不同层次上的存储器,通过适当的硬件、软件有机地组合在一起形成计算机的存储体系结构。例如,由高速缓存(Cache) .主存储器(MM)和辅助存储器构成的3层存储器层次结构存如下图所示。接近CPU的存储器容量更小、速度更快、成本更高,辅存容量大、速度慢,价格低。采用分级存储体系的目的是解决存储的容量、价格和速度之间的矛盾。

CPU的工作频率((主频)包括两个部分:外频与倍频,两者的乘积就是主频。

所谓外频,就是外部频率,指的是系统总线频率。

倍频的全称是倍频系数,倍频系数是指CPU主频与外频之间的相对比例关系。最初CPU主频和系统总线速度是一样的,但CPU的速度越来越快,倍频技术也就相应产生。它的作用是使系统总线工作在相对较低的频率上,而CPU速度可以通过倍频来提升。

RTOS

任务是RTOS中最重要的操作对象,每个任务在RTOS的调度下由CPU分时执行。任务的调度目前主要有时间分片式、轮流查询式和优先抢占式三种,不同的RTOS可能支持其中一种或几种,其中优先抢占式对实时性的支持最好。

在非实时系统中,调度的主要目的是缩短系统平均响应时间,提高系统资源的利用率,或优化某一项指标;而实时系统中调度的目的则是要尽可能地保证每个任务满足他们的时间约束,及时对外部请求做出响应。

总线

总线是一组能为多个部件分时共享的信息传送线,用来连接多个部件并为之提供信息交换通路。所谓共享,指连接到总线上的所有部件都可通过它传递信息;分时性指某一时刻只允许一个部件将数据发送到总线上。因此,共享是通过分时实现的。

CPU访问内存

CPU访问内存通常是同步方式,CPU与I/O接口交换信息通常是同步方式,CPU与PCI总线交换信息通常是同步方式,I/O接口与打印机交换信息则通常采用基于缓存池的异步方式。

DMA方式是一种不经过CPU而直接在外设与内存间进行的数据交换控制方式。在DMA模式下,CPU只需向DMA控制器下达命令,让DMA控制器来处理数据的传送,数据传送完之后再把信息反馈给CPU即可。

(1)控制器。控制器是分析和执行指令的部件,也是统一指挥并控制计算机各部件协

调工作的中心部件,所依据的是机器指令。控制器的组成包含如下。

① 程序计数器 PC:存储下一条要执行指令的地址;

② 指令寄存器 IR:存储即将执行的指令;

③ 指令译码器 ID:对指令中的操作码字段进行分析解释;

④ 时序部件:提供时序控制信号。

**(2)运算器。运算器也称为算术逻辑单元(ArithmeticandLogicUnit,ALU),其主要功

能是在控制器的控制下完成各种算术运算和逻辑运算。运算器的组成包含如下。**

① 算术逻辑单元 ALU:数据的算术运算和逻辑运算;

② 累加寄存器 AC:通用寄存器,为 ALU 提供一个工作区,用在暂存数据;

③ 数据缓冲寄存器 DR:写内存时,暂存指令或数据;

④ 状态条件寄存器 PSW:存状态标志与控制标志(争议点:也有将其归为控制器的)

精简指令系统计算机(RISC)的特点主要包括:

选取使用频率最高的一些简单指令,以及很有用但不复杂的指令。

指令长度固定,指令格式种类少,寻址方式种类少。

只有取数/存数指令访问存储器,其余指令的操作都在寄存器之间进行。

大部分指令在一个机器周期内完成。

CPU中通用寄存器数量相当多。

以硬布线控制为主,不用或少用微指令码控制。

复杂指令系统计算机(CISC)的特点主要有:

指令系统复杂,指令数目多达200~3000条。

指令长度不固定,有更多的指令格式和更多的寻址方式。

CPU内部的通用寄存器比较少。

有更多的可以访问主存的指令。

指令种类繁多,但各种指令的使用频度差别很大。

不同的指令执行时间相差很大,一般都需要多个时钟周期才能完成。

控制器大多采用微程序控制器来实现。

难以用优化编译的方法获得高效率的目的代码。

双缓冲区(double buffering)的主要特点如下:

两个缓冲区,一个用于存储数据,另一个用于准备下一次的数据处理或传输。

当一个缓冲区在数据处理过程中被填满时,另一个缓冲区用于准备下一次的数据处理或传输。

缓冲区的切换是由硬件或软件自动完成的,不需要人工干预。

通过这种方式,可以避免数据丢失或重复传输的问题,同时提高数据处理的效率和稳定性。

流水线

流水线技术把一个任务分解为若干顺序执行的子任务,不同的子任务由不同的执行机构负责执行,而这些机构可以同时并行工作。在任一时刻,任一任务只占用其中一个执行机构,这样就可以实现多个任务的重叠执行,以提高工作效率。

流水线周期

流水线应用过程中,会将需要处理的工作分为 N 个阶段,最耗时的那一段所消耗的时间为流水线周期。如:使用流水线技术执行 100 条指令,每条指令取指 2ms,分析 4ms,执行 1ms,则流水线周期为 4ms。

计算流水线执行时间

延续上面的场景,将 1 个任务的执行过程可分成 N 个阶段,假设每个阶段完成时间为 t,则完成该任务所需的时间即为 Nt。若以传统的方式,则完成 k 个任务所需的时间是kNt;而使用流水线技术执行,且花费的时间是 Nt+(k-1)t。也就是说,除了第 1 个任务需要完整的时间外,其他都通过并行,节省下了大量的时间。所以流水线的执行时间可通俗的表达为:流水线执行时间=第 1 条指令的执行时间+(n-1)*流水线周期

注:n 代表需要处理的任务数量。

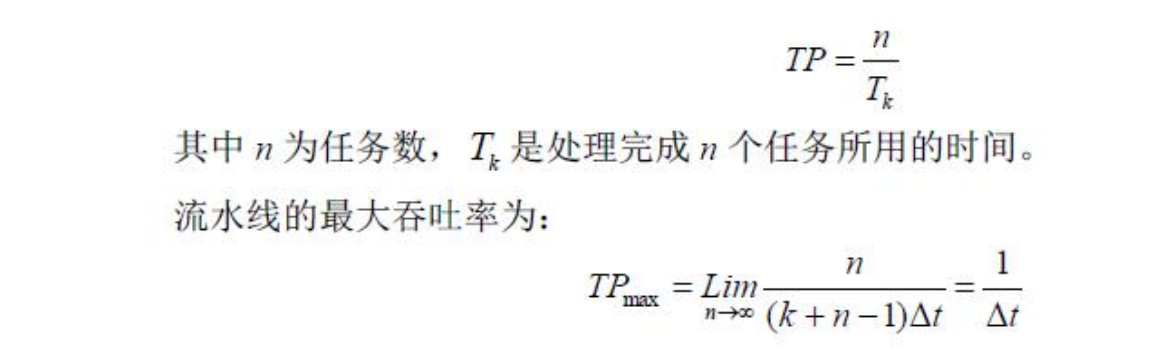

流水线的吞吐率

流水线的吞吐率(代表实际完成情况. Though Put rate,TP)是指在单位时间内流水线所完成的任务数量或输出的结果数量。有些文献也称为平均吞吐率、实际吞吐率。计算流水线吞吐率的最基本的公式如下:

流水线的吞吐率 代表实际完成情况

流水线最大吞吐率 代表最快速度 1/t

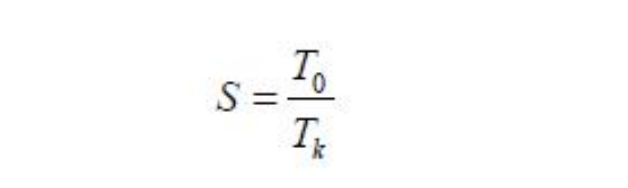

流水线的加速比

流水线的加速比>1

最大加速比 S=K

在流水线中,因为在同一时刻,有多个任务在重叠地执行,虽然完成一个任务的时间与单独执行该任务相近(甚至由于分段的缘故,可能更多一些),但是从整体上看完成多个任务所需的时间则大大减少。完成同样一批任务,不使用流水线所用的时间与使用流水线所用的时间之比称为流水线的加速比(speedup ratio)。如果不使用流水线,即顺序执行所用的时间为 T0 ,使用流水线的执行时间为 Tk ,则计算流水线加速比的基本公式如下:

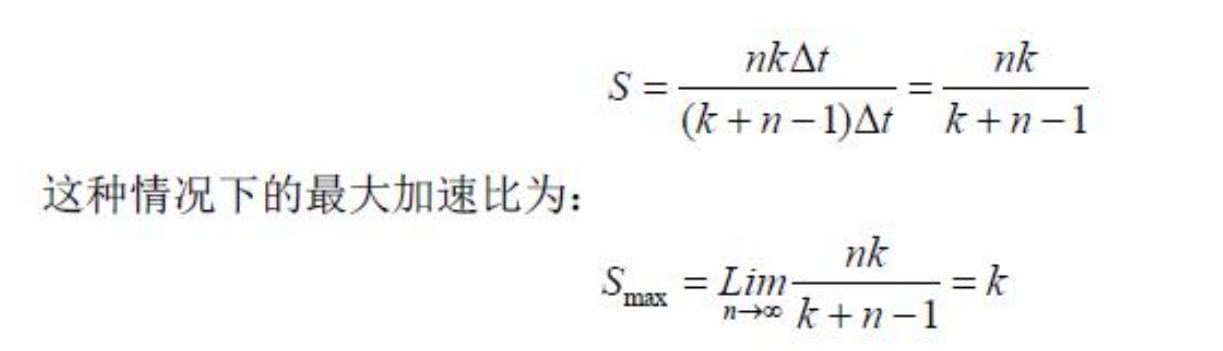

如果流水线各个流水段的执行时间都相等(设为 Dt),则一条 k 段流水线完成 n 个连续任务所需要的时间为(k+n-1)Dt。如果不使用流水线,即顺序执行这 n 个任务,则所需要的时间为 nkDt。因此,各个流水段执行时间均相等的一条 k 段流水线完成 n 个连续任务时的实际加速比为:

嵌入式系统设计

嵌入式系统的存储部件中,存取速度最快的是寄存器组。

越接近CPU的存储不见访问速度越快。存储速度从快到慢分别是:寄存器组、Cache、内存、Flash。

嵌入式系统中采用中断方式实现输入输出的主要原因是能对突发事件做出快速响应。在中断时,CPU断点信息一般保存到栈中。

嵌入式微处理器

嵌入式微处理器(MPU)是嵌入式系统硬件层的核心,大多工作在为特定用户群专用设计的系统中,它将通用CPU中许多由板卡完成的任务集成在芯片内部,从而有利于嵌入式系统在设计时趋于小型化,同时还具有很高的效率和可靠性。嵌入式微控制器(Embedded Microcontroller Unit,EMCU)的典型代表是单片机,单片机从诞生之日起,称为嵌入式微控利命。P壮学由主紧凑,作为一个部件安装在所控制的装置中,主要执行信号控制的功能。数字信号处理器(digital signal processor)由大规模或超大规模集成电路芯片组成,是用来完成某种信号处理任务的处理器。它是为适应高速实时信号处理任务的需要还刚o长5公E数字集成电路技术和委字信与灶—E’I外理能力信号处理器的头块门rN’不断提高。片上系统(System-on-a-chip)指的是在单个芯片上集成一个完整的系统,一般包括中央处理器(CPU)、存储器,以及外围电路等SOC是与其他技术并行发展的,如绝缘硅(SOI) ,它可以提供增强的时钟频率,从而降低微芯片的功耗。

嵌入式数据库系统

嵌入式系统的数据库系统称为嵌入式数据库系统或嵌入式实时数据库系统。嵌入式系统必须能够在没有人工干预的情况下,长时间不间断地运行,因此要求高的可靠性。同时要求数据库操作具备可预知性,而且系统的大小和性能也都必须是可预知的,以保证系统的性能。嵌入式系统需要与底层硬件打交道,因此在数据管理时,也要有底层控制的能力,如什么时候会发生磁盘操作,磁盘操作的次数,如何控制等。底层控制的能力是决定数据库管理操作的关键。

嵌入式数据库管理系统一般只提供本机服务接口,为前端应用提供基本的数据支持。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)