DS18B20温度传感器VHDL数码管显示DE2-115开发板代码下载

名称:DS18B20温度传感器DE2-115开发板数码管显示VHDL软件:Quartus II语言:VHDL代码功能:1、正常温度范围显示2、按一下按键实现测温,数码管显示温度3、温度正常时绿色led灯亮,异常时红色led灯亮FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com本代码已在DE2-115开发板验证,开发板如下,其他开发板可以修改管脚适配:

·

名称:DS18B20温度传感器DE2-115开发板数码管显示VHDL

软件:Quartus II

语言:VHDL

代码功能:

1、正常温度范围显示

2、按一下按键实现测温,数码管显示温度

3、温度正常时绿色led灯亮,异常时红色led灯亮

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

本代码已在DE2-115开发板验证,开发板如下,其他开发板可以修改管脚适配:

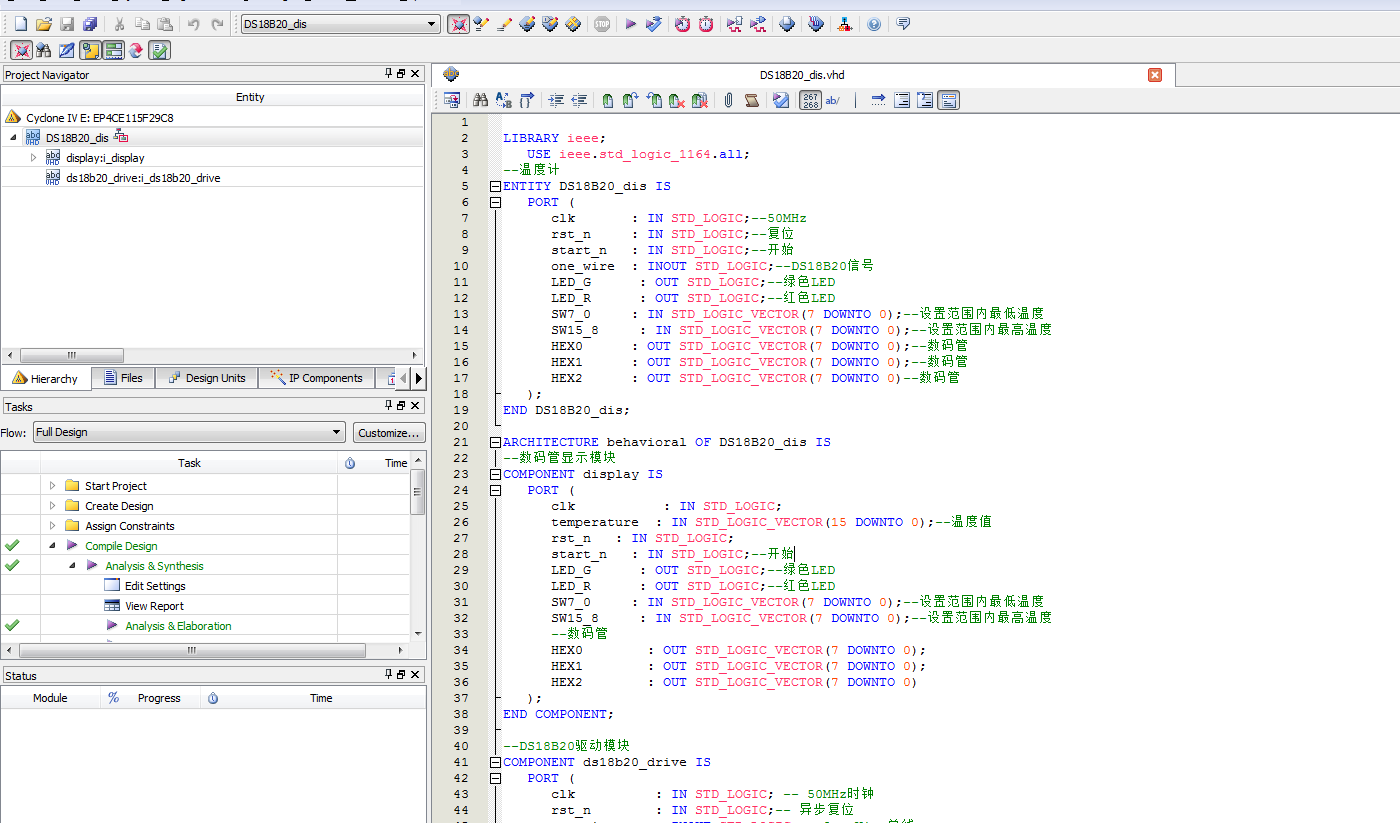

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; USE ieee.std_logic_arith.all; --BS18B20驱动模块 ENTITY ds18b20_drive IS PORT ( clk : IN STD_LOGIC; -- 50MHz时钟 rst_n : IN STD_LOGIC;-- 异步复位 one_wire : INOUT STD_LOGIC;-- One-Wire总线 temperature : OUT STD_LOGIC_VECTOR(15 DOWNTO 0) -- 输出温度值 ); END ds18b20_drive; ARCHITECTURE behavioral OF ds18b20_drive IS constant S00 : STD_LOGIC_VECTOR(4 DOWNTO 0):="00000"; constant S0 : STD_LOGIC_VECTOR(4 DOWNTO 0):="00001"; constant S1 : STD_LOGIC_VECTOR(4 DOWNTO 0):="00010"; constant S2 : STD_LOGIC_VECTOR(4 DOWNTO 0):="00011"; constant S3 : STD_LOGIC_VECTOR(4 DOWNTO 0):="00100"; constant S4 : STD_LOGIC_VECTOR(4 DOWNTO 0):="00101"; constant S5 : STD_LOGIC_VECTOR(4 DOWNTO 0):="00110"; constant S6 : STD_LOGIC_VECTOR(4 DOWNTO 0):="00111"; constant S7 : STD_LOGIC_VECTOR(4 DOWNTO 0):="01000"; constant WRITE0 : STD_LOGIC_VECTOR(4 DOWNTO 0):="01001"; constant WRITE1 : STD_LOGIC_VECTOR(4 DOWNTO 0):="01010"; constant WRITE00 : STD_LOGIC_VECTOR(4 DOWNTO 0):="01011"; constant WRITE01 : STD_LOGIC_VECTOR(4 DOWNTO 0):="01100"; constant READ0 : STD_LOGIC_VECTOR(4 DOWNTO 0):="01101"; constant READ1 : STD_LOGIC_VECTOR(4 DOWNTO 0):="01110"; constant READ2 : STD_LOGIC_VECTOR(4 DOWNTO 0):="01111"; constant READ3 : STD_LOGIC_VECTOR(4 DOWNTO 0):="10000"; SIGNAL cnt : STD_LOGIC_VECTOR(5 DOWNTO 0); SIGNAL clk_1us : STD_LOGIC; SIGNAL cnt_1us : STD_LOGIC_VECTOR(19 DOWNTO 0); SIGNAL cnt_1us_clear : STD_LOGIC; SIGNAL state : STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL one_wire_buf : STD_LOGIC;-- One-Wire总线 缓存寄存器 SIGNAL temperature_buf : STD_LOGIC_VECTOR(15 DOWNTO 0);-- 采集到的温度值缓存器 SIGNAL step : STD_LOGIC_VECTOR(5 DOWNTO 0); -- 子状态寄存器 0~50 SIGNAL bit_valid : STD_LOGIC_VECTOR(3 DOWNTO 0); -- 有效位 SIGNAL t_buf : STD_LOGIC_VECTOR(15 DOWNTO 0); BEGIN --++++++++++++++++++++++++++++++++++++++ -- 分频器50MHz->1MHz 开始 --++++++++++++++++++++++++++++++++++++++ PROCESS (clk, rst_n) BEGIN IF ((NOT(rst_n)) = '1') THEN cnt <= "000000"; ELSIF (clk'EVENT AND clk = '1') THEN IF (cnt = "110001") THEN cnt <= "000000"; ELSE cnt <= cnt + "000001";-- 计数子 END IF; END IF; END PROCESS; PROCESS (clk, rst_n) BEGIN IF ((NOT(rst_n)) = '1') THEN clk_1us <= '0'; -- 1MHz 时钟 ELSIF (clk'EVENT AND clk = '1') THEN IF (cnt <= "011000") THEN -- 24 = 50/2 - 1 clk_1us <= '0'; ELSE clk_1us <= '1'; END IF; END IF; END PROCESS; ---------------------------------------- -- 分频器50MHz->1MHz 结束 ---------------------------------------- --++++++++++++++++++++++++++++++++++++++ -- 延时模块 开始 --++++++++++++++++++++++++++++++++++++++ PROCESS (clk_1us) BEGIN IF (clk_1us'EVENT AND clk_1us = '1') THEN IF (cnt_1us_clear = '1') THEN -- 请1us延时计数子 cnt_1us <= "00000000000000000000"; ELSE cnt_1us <= cnt_1us + "00000000000000000001";-- 1us延时计数子 END IF; END IF; END PROCESS; ---------------------------------------- -- 延时模块 结束 ---------------------------------------- --++++++++++++++++++++++++++++++++++++++ -- DS18B20状态机 开始 --++++++++++++++++++++++++++++++++++++++ --++++++++++++++++++++++++++++++++++++++ PROCESS (clk_1us, rst_n) BEGIN IF ((NOT(rst_n)) = '1') THEN one_wire_buf <= 'Z'; step <= "000000"; state <= S00; -- 状态寄存器 ELSIF (clk_1us'EVENT AND clk_1us = '1') THEN CASE state IS WHEN S00 => temperature_buf <= "0000000000011111"; state <= S0; WHEN S0 =>-- 初始化 cnt_1us_clear <= '1'; one_wire_buf <= '0'; state <= S1; WHEN S1 => -- 延时500us cnt_1us_clear <= '0'; IF (cnt_1us = "00000000000111110100") THEN cnt_1us_clear <= '1'; one_wire_buf <= 'Z';-- 释放总线 state <= S2; END IF; WHEN S2 => cnt_1us_clear <= '0'; IF (cnt_1us = "00000000000001100100") THEN -- 等待100us cnt_1us_clear <= '1'; state <= S3; END IF; WHEN S3 => IF ((NOT(one_wire)) = '1') THEN -- 若18b20拉低总线,初始化成功 state <= S4; ELSIF (one_wire = '1') THEN -- 否则,初始化不成功,返回S0 state <= S0; END IF; WHEN S4 => cnt_1us_clear <= '0'; IF (cnt_1us = "00000000000110010000") THEN-- 再延时400us cnt_1us_clear <= '1'; state <= S5; END IF; WHEN S5 => -- 写数据 IF (step = "000000") THEN -- 0xCC step <= step + "000001"; state <= WRITE0; ELSIF (step = "000001") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "000010") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "000011") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "000100") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "000101") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "000110") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "000111") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "001000") THEN-- 0x44 step <= step + "000001"; state <= WRITE0; ELSIF (step = "001001") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "001010") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "001011") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "001100") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "001101") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "001110") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "001111") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "010000") THEN -- 第一次写完,750ms后,跳回S0 one_wire_buf <= 'Z'; step <= step + "000001"; state <= S6; ELSIF (step = "010001") THEN -- 再次置数0xCC和0xBE step <= step + "000001";-- 0xCC state <= WRITE0; ELSIF (step = "010010") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "010011") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "010100") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "010101") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "010110") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "010111") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "011000") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "011001") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "011010") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "011011") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "011100") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "011101") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "011110") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "011111") THEN step <= step + "000001"; state <= WRITE0; ELSIF (step = "100000") THEN one_wire_buf <= '0'; step <= step + "000001"; state <= WRITE01; ELSIF (step = "100001") THEN-- 第二次写完,跳到S7,直接开始读数据 step <= step + "000001"; state <= S7; END IF; WHEN S6 => cnt_1us_clear <= '0'; IF (cnt_1us = "10110111000110110000" OR one_wire = '1') THEN -- 延时750ms!!!! cnt_1us_clear <= '1'; state <= S0; -- 跳回S0,再次初始化 END IF; WHEN S7 => -- 读数据 IF (step = "100010") THEN bit_valid <= "0000"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "100011") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "100100") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "100101") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "100110") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "100111") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "101000") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "101001") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "101010") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "101011") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "101100") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "101101") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "101110") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "101111") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "110000") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "110001") THEN bit_valid <= bit_valid + "0001"; one_wire_buf <= '0'; step <= step + "000001"; state <= READ0; ELSIF (step = "110010") THEN step <= "000000"; state <= S0; END IF; --++++++++++++++++++++++++++++++++ -- 写状态机 --++++++++++++++++++++++++++++++++ WHEN WRITE0 =>-- 输出0 cnt_1us_clear <= '0'; one_wire_buf <= '0'; IF (cnt_1us = "00000000000001010000") THEN -- 延时80us cnt_1us_clear <= '1'; one_wire_buf <= 'Z';-- 释放总线,自动拉高 state <= WRITE00; END IF; WHEN WRITE00 => -- 空状态 state <= S5; WHEN WRITE01 =>-- 空状态 state <= WRITE1; WHEN WRITE1 => cnt_1us_clear <= '0'; one_wire_buf <= 'Z';-- 输出1 释放总线,自动拉高 IF (cnt_1us = "00000000000001010000") THEN cnt_1us_clear <= '1';-- 延时80us state <= S5; END IF; ---------------------------------- -- 写状态机 ----------------------------------

设计文档:

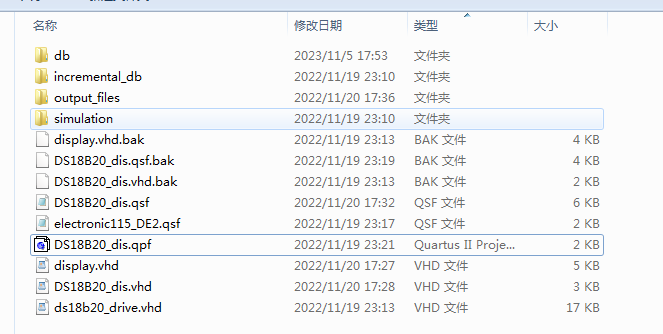

工程文件

程序文件

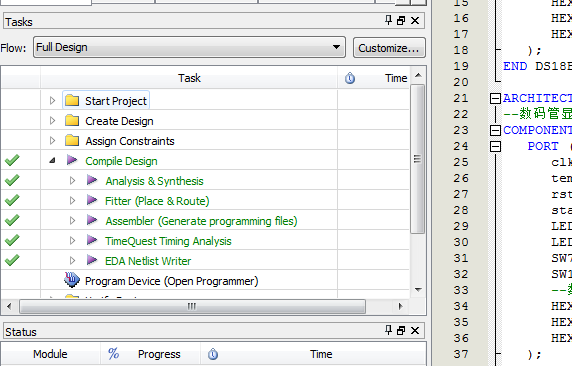

程序编译

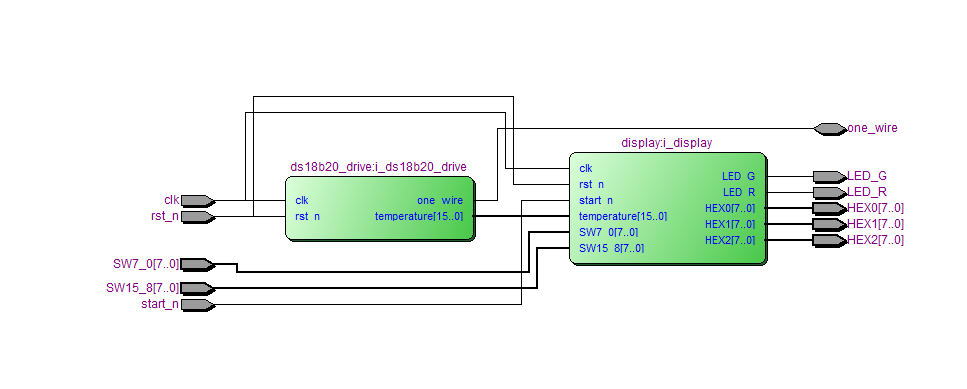

RTL图

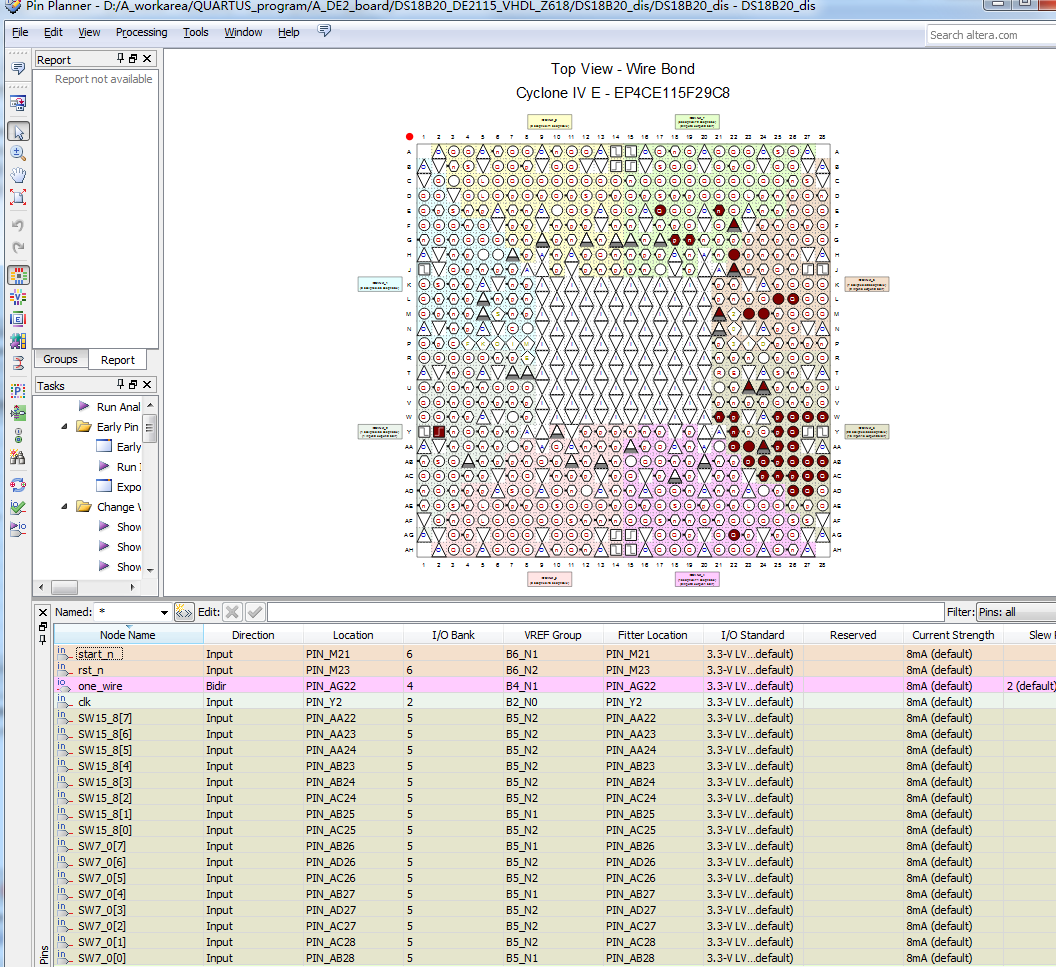

管脚分配

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=261

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=261

所有评论(0)