软考嵌入式 1:计算机系统基础知识

1.计算机系统基础知识1.1数制及其转换1.1.1二进制、八进制、十进制和十六进制等常用数制及其相互转换1.2数据的表示1.2.1数值的原码、反码、补码、移码表示,定点数和浮点数,精度和溢出1.2.2字符、汉字、声音、图像的编码方式1.2.3校验方法和校验码(奇偶校验码、海明校验码、循环冗余校验码等)1.3算术运算和逻辑运算。

1.计算机系统基础知识

1.1数制及其转换

1.1.1二进制、八进制、十进制和十六进制等常用数制及其相互转换

1.2数据的表示

1.2.1数值的原码、反码、补码、移码表示,定点数和浮点数,精度和溢出

1.2.2字符、汉字、声音、图像的编码方式

1.2.3校验方法和校验码(奇偶校验码、海明校验码、循环冗余校验码等)

1.3算术运算和逻辑运算

1.3.1二进制数运算方法

1.3.2逻辑代数的基本运算和逻辑表达式的化简

1.4计算机组成及主要部件的基本工作原理

1.4.1CPU的组成和基本工作原理

1.4.2常用I/O设备、通信设备的性能以及基本工作原理

1.4.3I/O接口的功能、类型和特点

1.5计算机体系结构

1.5.1CISC、RISC、流水线技术和超标量等

1.5.2多处理机、并行处理和分布处理

1.5.3冯・诺依曼结构与哈佛结构

1.6可靠性与系统性能评测基础知识

1.6.1诊断与容错

•故障检测

•容错技术与容错控制

1.6.2系统可靠性的分析与评价

•系统可靠性的定义

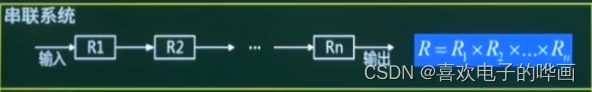

•串联系统的特点及可靠性度量

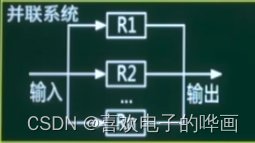

•并联系统的特点及可靠性度量

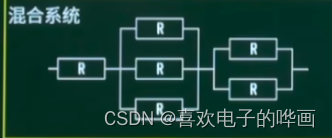

•N 模冗余系统等可靠性模型的特点

1.6.3计算机系统性能的评测方法

•平均无故障时间的定义及计算

•平均修复时间的定义及计算

•可用性的定义及计算

1.1 数制及其转换

1.1.1 二进制、八进制、十进制和十六进制等常用数制及其相互转换

- 二进制是最基本的数字系统,计算机内部使用二进制(0和1)进行所有的计算和数据存储。

- 八进制和十六进制主要用于简化二进制数的表示,其中十六进制因为与二进制的转换特别直接而广泛使用于计算机科学中。

- 十进制是我们日常生活中使用的数字系统。

转换方法:

-

N进制转换10进制用按权展开:每位的位权相乘再相加

-

10进制转换N进制用短除法:除N,再倒取余数

1.2 数据的表示

数据存储:8b(Bit位)=1B(Byte字节),1KB==1024B,1MB=

=1024KB,1GB=

=1024MB,1TB=

=1024GB

1.2.1 数值的原码、反码、补码、移码表示,定点数和浮点数,精度和溢出

- 原码:直接表示正负号和数值。范围:

- 反码:正数的反码与原码相同,负数的反码是其原码除符号位外所有位取反。

- 补码:正数的补码与原码相同,负数的补码是其反码加1。在计算机中,使用补码是为了简化加法和减法运算。(补码的+0和-0都是00000000,补码表示0只有一种编码)

- 移码:是将补码的符号位也取反,常用于浮点数的表示。

- 定点数:小数点位置固定的数值表示方法。

- 浮点数:用于表示非常大或非常小的数值,通过分开存储符号、指数和尾数来实现。数值范围由阶码决定,数值精度由尾数决定

。M是尾数,e是指数(阶码),R为基数(计算机固定为2),

-

阶符 阶码 数符 尾数 -

IEEE754

S R M 符号位

1位

阶码用移码表示(偏移量+127,+1023,+16383)

单精度8位

双精度11位

扩充精度15位

尾数,左边隐含一个1

单精度23位

双精度52位

扩充精度64位

精度和溢出:

- 精度指的是计算机能够区分和表示的最小数值差异。

- 溢出是指计算结果超出了计算机可表示的数值范围。

1.2.2 字符、汉字、声音、图像的编码方式

- 字符:通常通过ASCII码或Unicode等编码方式表示。

- 汉字:在计算机中通过GB2312、GBK、或UTF-8等编码方式表示。

- 声音:通过模拟信号数字化(如PCM编码)来表示。

- 图像:通过将图像分成像素网格,并为每个像素指定颜色值(通常使用RGB编码)来表示。

1.2.3 校验方法和校验码

- 奇偶校验码:通过在数据中添加一位校验位,使得总的1的位数为奇数(奇校验)或偶数(偶校验),用于错误检测。

- 海明校验码:利用多个校验位,以一种方式分布于数据位中,不仅可以检测错误,还能确定单个错误位的位置。

,k是校验位数,n是数据位数

- 循环冗余校验码(CRC):通过将数据视为一个大的多项式并对其进行除法运算,得到的余数作为CRC,用于错误检测。

1.3.1 二进制数运算方法

二进制运算是计算机进行算术运算的基础,包括加法、减法、乘法和除法。

- 加法:遵循逐位相加的原则,0+0=0,0+1=1,1+0=1,1+1=10(进位)。

- 减法:使用补码进行操作,即被减数加上减数的补码。

- 乘法:类似于十进制乘法,但更简单,只涉及0和1的乘法和位的移动。

- 除法:使用除数持续减去被除数,直到差小于除数,过程中记录减法操作的次数。

1.3.2 逻辑代数的基本运算和逻辑表达式的化简

- 基本逻辑运算:与(AND)(符号

)有0得0全1为1;或(OR)(符号

)有1得1全0为0;非(NOT)取反0变1,1变0;异或(XOR)(符号

) 相同为0,不同为1。

- 逻辑非 ! 的优先级最高

- 逻辑与 && 次之

- 逻辑或 || 优先级最低

- 逻辑表达式化简:使用德摩根定律、分配律、结合律等逻辑代数规则来简化逻辑表达式,以减少所需的逻辑门数量。

做题知识点:内存容量=终地址-始地址+1编制(地址的数据容量),多少片能构成时:总片数=总容量

每片的容量

1.4 计算机组成及主要部件的基本工作原理

计算机硬件由运算器、控制器、存储器、输入\输出设备组成

1.4.1 CPU的组成和基本工作原理

- CPU(中央处理单元):计算机的大脑,负责解释和执行指令。主要由运算器、控制器和寄存器组和内部总线组成。

- 运算器:由算术逻辑单元ALU、累加寄存器AC、数据缓冲寄存器DR、状态条件寄存器PSW组成

- 控制器:由程序寄存器PC、指令寄存器IR、地址寄存器AR、指令译码器ID组成

ALU (算术逻辑单元):CPU的计算引擎,负责执行算术和逻辑操作。

AC (累加寄存器):临时存储ALU运算结果的寄存器。

DR (数据缓冲寄存器):在数据从内存传输到CPU时或从CPU传输到内存时暂存数据的寄存器。

PSW (状态条件寄存器):记录CPU运行状态(如零标志、进位标志等)的寄存器。

PC (程序计数器):存放下一条要执行的指令在内存中的地址。

IR (指令寄存器):存放当前正在执行的指令。

AR (地址寄存器):存放指令或数据的内存地址。

ID (指令译码器):解析当前指令并确定所需的操作和操作数

CPU性能指标:主频、字长、CPU缓存、核心数量

总线分为数据、控制、地址总线。性能指标:带宽、位宽、工作频率。同一时刻仅允许一个设备发送,但允许多个设备接收;

系统性能评测:时钟频率、指令执行MIPS、等效指令速度法、数据处理速率(PDR)、核心程序法、基准测试程序法

额外知识点

计算机指令:一条指令由操作码和操作数两部分组成;

指令寻址方式分顺序寻址和跳跃寻址

指令操作数的寻址方式有

- 立即寻址:操作数直接包含在指令中,不需要访问内存。

- 直接寻址:指令包含操作数的直接内存地址。

- 间接寻址:指令指向一个内存地址,该地址中存储着最终操作数的实际地址。

- 寄存器寻址:指令的操作数在寄存器中,而非在内存中。

- 基址寻址:操作数地址由基址寄存器的值加上指令中给出的偏移量来确定。

- 变址寻址:操作数地址由变址寄存器中的值加上指令中给出的偏移量来确定,常用于实现数组。

- 相对寻址:指令提供一个偏移量,该偏移量与程序计数器的当前值相加,得到操作数的地址。

1.4.2 常用I/O设备、通信设备的性能以及基本工作原理

- 输入设备(如键盘、鼠标)允许用户与计算机交互。

- 输出设备(如显示器、打印机)向用户展示数据和信息。

- 通信设备(如调制解调器、网络卡)使计算机能够与外界通信,发送和接收数据。

输入输出设备管理方式有:

直接程序控制、中断方式、直接存储器存取方式(DMA)、输入输出处理机(IOP)

DMA控制器里面包含地址寄存器、状态寄存器、控制寄存器、字节计数器。

- 地址寄存器包括源地址和目的地址寄存器

- 状态寄存器用于寄存DMA传送前后的状态

- 控制寄存器用于选择DMA控制器的操作类型、工作方式、 传送方向和有关参数;

- 字节计数器用于控制传送数据块的长度。

1.4.3 I/O接口的功能、类型和特点

- I/O接口:连接I/O设备与计算机主机。它协调主机与设备之间的数据传输,提供电压转换、缓冲等功能。

1.5 计算机体系结构

1.5.1 CISC、RISC、流水线技术和超标量等

- CISC(复杂指令集计算机)和RISC(精简指令集计算机)是两种主要的CPU设计哲学。

- 流水线技术:将指令执行分解为多个步骤(

取指

分析

执行

),每个步骤由不同的处理单元处理,提高执行速度。

流水线周期:执行时间最长的一段

流水线总执行时间:1条指令总执行时间+(总指令条数-1)*流水线周期实践公式(不常用):

流水线吞吐量(TP):指令条数/流水线执行时间,,最大吞吐量是流水线周期的倒数

-

数据冒险:这种冒险发生在当流水线的后续指令需要前面某个指令的执行结果作为输入,但由于流水线的并行性,那个必需的结果还没有被计算出来。换句话说,它是由于指令之间的数据依赖性导致的。解决数据冒险的技术包括数据前递(data forwarding)或数据旁路(data bypassing)、阻塞(stalling)以及指令重排(instruction reordering)等。

-

结构冒险:如前所述,结构冒险发生在当两个或更多的指令在同一时间尝试使用同一个资源(比如内存或I/O设备)时。由于资源在任一时刻只能被一个指令访问,这就导致了冲突和延迟。增加资源、分时访问资源等策略可用于解决结构冒险。

-

控制冒险:控制冒险发生在由于控制指令(如跳转和分支指令)导致的程序执行路径改变时。在流水线处理器中,由于指令是并行执行的,控制指令的目标地址可能还没有被确定,但下一个指令已经在执行了。这时,如果控制指令的执行改变了执行路径,那么那些已经在执行的指令可能就不再需要了,这导致了处理器时间的浪费。解决控制冒险的技术包括分支预测(branch prediction)、延迟分支(delayed branching)等。

- 超标量架构:能够同时执行多个指令,提高处理性能

1.5.2 多处理机、并行处理和分布处理

- 多处理机:在一个系统中使用多个处理器来提高计算速度。

- 并行处理:同时执行多个计算任务,以提高效率和处理速度。

- 分布处理:使用网络连接的多个计算机系统共同完成任务。

1.5.3 冯·诺依曼结构与哈佛结构

- 冯·诺依曼结构:一种计算机架构设计,指令和数据存储在同一内存中,通过一个总线进行通信。

- 哈佛结构:指令和数据分别存储在不同的内存中,可以同时访问指令和数据,提高速度。

Cache

- 功能:提高CPU数据输入输出的速率,突破所谓的“冯·诺依曼瓶颈”

- 速度:在计算机存储结构中,Cache是访问较快的层次

- 原理:使用Cache改善系统性能的依据是程序的局部性原理

- 组成:Cache由两部分组成:控制部分和Cache存储器部分

- 平均系统周期时间:

,h是Cache命中率、t1是Cache周期时间、t2是主存储器周期时间、系统平均周期t3

1.6 可靠性与系统性能评测基础知识

1.6.1 诊断与容错

- 故障检测:通过各种技术识别系统中的错误或故障。

- 容错技术与容错控制:使系统能够在部分组件失败时继续运行。

1.6.2 系统可靠性的分析与评价

- 系统可靠性定义:系统在规定条件和时间内无故障运行的能力。

- 串联和并联系统:串联系统的可靠性低于单个组件,而并联系统的可靠性高于单个组件。

- N模冗余系统:通过复制关键组件来提高系统的可靠性。

串联系统可靠性计算:

并联系统可靠性计算:

混合系统可靠性计算:

1.6.3 计算机系统性能的评测方法

- 平均无故障时间(MTBF):系统预期在故障之间运行的时间。

- 平均修复时间(MTTR):修复系统故障所需的平均时间。

- 可用性:系统在特定时间内正常运行和可用的比例。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)