SRAM测试试验设计Verilog代码VIVADO ARTIX-7开发板

SRAM测试试验测试SRAM接口,本试验用来试验SRAM的读写功能,通过在线调试工具观察读写的数据,并进行读写数据比对。

名称:SRAM测试试验设计Verilog代码VIVADO ARTIX-7开发板(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

SRAM测试试验

测试SRAM接口,本试验用来试验SRAM的读写功能,通过在线调试工具观察读写的数据,并进行读写数据比对。

本代码已在ARTIX-7开发板验证,ARTIX-7开发板如下,其他开发板可以修改管脚适配:

1简介

本试验用来试验SRAM的读写功能,通过在线调试工具观察读写的数据,并进行读写数据比对。

2实验原理

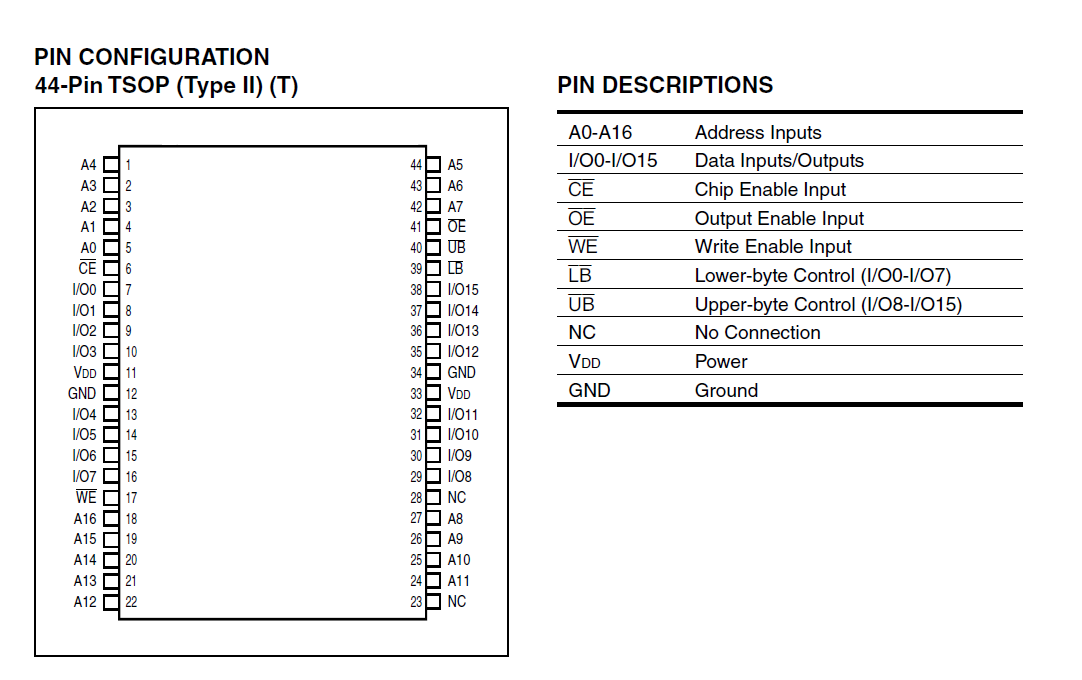

静态数据存储器SRAM是存储数据比较重要的器件,它由锁存器阵列构成。SRAM外部接口包括片选端口,读允许端口,写允许端口,地址端口,数据输出输入端口。在读写数据时,SRAM根据地址信号,经由译码电路选择读写的相对应的存储单元。我们开发板选择的SRAM型号是IS61WV12816EDBLL,可存储128K的数据,其管脚定下如下:

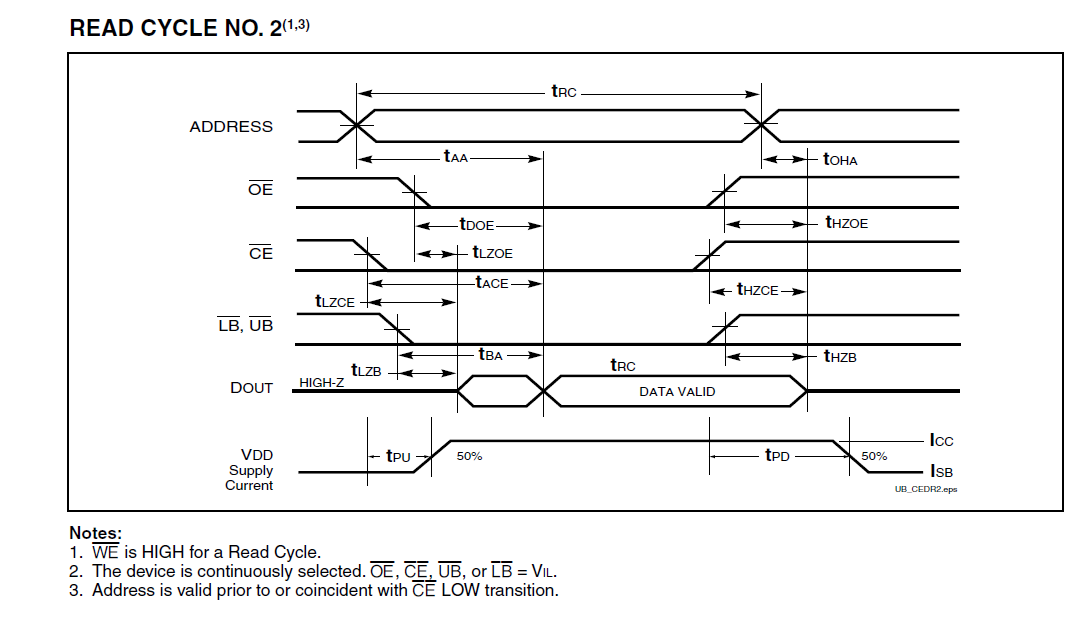

其时序如下图所示:

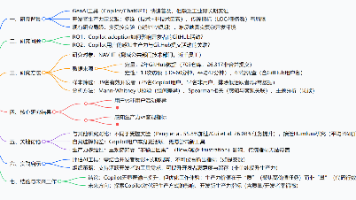

3程序设计

rst , //软复位信号

clk , //时钟信号

sram_ab , //sram的地址信号

sram_db , //sram双向数据信号

sram_wr , //sram写使能信号

sram_rd , //sram读使能信号

error, //用来数据比对,如果比对结果错误,则将error赋1,

task_start , //Start Testing ---LED1

task_finish

);

input rst ;

input clk ;

output [16:0] sram_ab ;

inout [15:0] sram_db ;

output sram_wr ;

output sram_rd ;

output error;

output task_start ;

output task_finish;

//ports

wire rst ;

wire clk ;

parameter IDLE = 3'D0,

WRITE_1 = 3'D1,

WRITE_2 = 3'D2,

READ_1 = 3'D3,

READ_2 = 3'D4;

assign sram_db = sram_rd ? sram_db_reg:'hz;

//计数用来产生25Mhz的时钟

reg [3:0] clk_count;

always @(posedge clk or negedge rst)

if(!rst)

begin

clk_count<=4'd0;

end

else

begin

clk_count<=clk_count+4'b1;

end

assign clk25m = clk_count[2];

//sram读写state machine

always @ (STATE or sram_ab or error or task_start)

begin

case(STATE)

IDLE : if(task_start)

NEXT = WRITE_1;

else

NEXT = IDLE ;

WRITE_1 : NEXT = WRITE_2;

WRITE_2 : if( sram_ab >= 17'h1ffff)

NEXT = READ_1;

else

NEXT = WRITE_1;

READ_1 : NEXT = READ_2;

READ_2 : if( sram_ab >= 17'h1ffff)//error ||

NEXT = IDLE;

else

NEXT = READ_1;

default : NEXT = IDLE ;

endcase

end

//registe the state

always @ (posedge clk25m or negedge rst)

if(!rst)

STATE <= IDLE;

else

STATE <= NEXT;

4实验现象

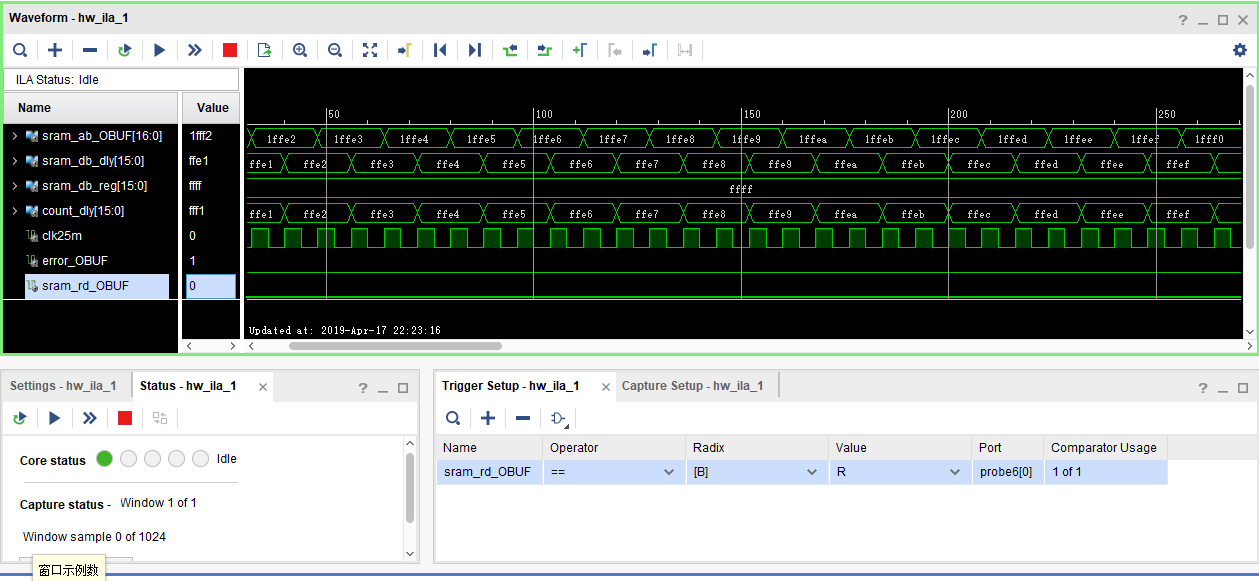

将目录“... \at7_prj_07\at7_prj\at7_prj.runs\impl_1”文件夹下的 at7_prj.bit 文件下载到开发板上,则sram开始自动读写操作,通过在线调试工具可以看到sram_rd信号为低电平时,表明FPGA在读SRAM数据,读出来的数据sram_db_dly与count_dly进行比对,数据一致,则说明sram读写正常,error信号一直是低电平。

部分代码展示:

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2019/04/13 17:54:08 // Design Name: // Module Name: at7_prj // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module at7_prj( rst , //软复位信号 clk , //时钟信号 sram_ab , //sram的地址信号 sram_db , //sram双向数据信号 sram_wr , //sram写使能信号 sram_rd , //sram读使能信号 error, //用来数据比对,如果比对结果错误,则将error赋1, task_start , //Start Testing ---LED1 task_finish ); input rst ; input clk ; output [16:0] sram_ab ; inout [15:0] sram_db ; output sram_wr ; output sram_rd ; output error; output task_start ; output task_finish; //ports wire rst ; wire clk ; (*mark_debug="TRUE"*)reg [16:0] sram_ab ; wire [15:0] sram_db ; (*mark_debug="TRUE"*) reg [15:0] sram_db_dly ; (*mark_debug="TRUE"*) reg sram_wr ; (*mark_debug="TRUE"*)reg sram_rd ; reg task_start ; reg task_finish; //internal signals reg clk_2; (*mark_debug="TRUE"*)wire clk25m; reg [2:0] STATE,NEXT; (*mark_debug="TRUE"*) reg error ; (*mark_debug="TRUE"*)reg [15:0] sram_db_reg; reg [15:0] count ; (*mark_debug="TRUE"*)reg [15:0] count_dly ; //parameters parameter IDLE = 3'D0, WRITE_1 = 3'D1, WRITE_2 = 3'D2, READ_1 = 3'D3, READ_2 = 3'D4; assign sram_db = sram_rd ? sram_db_reg:'hz; //计数用来产生25Mhz的时钟 reg [3:0] clk_count; always @(posedge clk or negedge rst) if(!rst) begin clk_count<=4'd0; end

源代码

点击下方的公众号卡片获取

更多推荐

已为社区贡献37条内容

已为社区贡献37条内容

所有评论(0)